尊敬的各位:

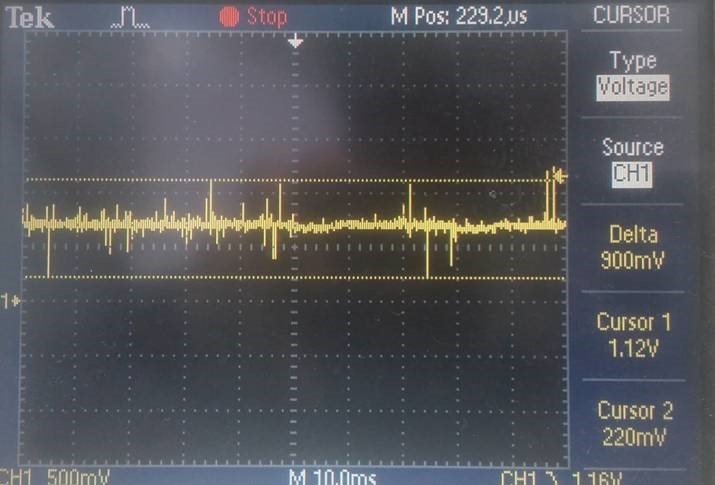

我们在TAS5751M的PBTL波形上遇到一些问题。

测试条件为PVcc=19V,RL=4ohm,PO=30W。

但有一个异常波形,比如在大约16W输出时的波形夹。

我们认为PCB布局存在一些问题,因为此原理图与EVM的原理图相同。

此外,TAS5751M EVM也没有出现故障。

请查看此PCB布局和异常波形夹,然后告诉我解决方案。

1.示意图

2.波形

e2e.ti.com/.../Abnormal-PBTL-waveform.mp4

3.布局

e2e.ti.com/.../main_5F00_v01_5F00_2017.1012万.pcb

此致

Jeffrey