您好~

我用音频精度测试以下代码(数字串行:输出;模拟:输入)

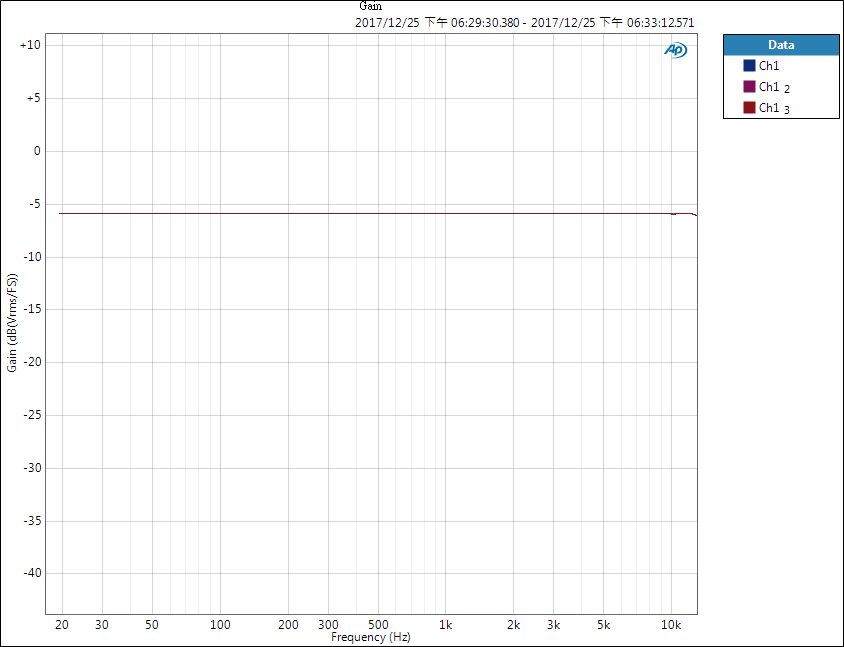

我得到的频率响应是-6dB,组延迟低于数据表建议的值。(数据表中提到组延迟(典型?) =13/FS,过滤器C外壳。

我的测量中的组延迟为0.33ms~11/fs?!.)

为确保正确,我的代码是否有任何可能的错误? (AP中的测量设置似乎正常,因为测试其他编解码器时没有问题。)

PS。 我使用4M晶体输入到MCLK引脚。 编解码器将BCLK和WCLK时钟输出到Audio Precision数字串行端口。 整个代码适用于32k采样率应用。

{0x00,0x00},// 0。 初始化到第0页

{0x01,0x01},// 1。 通过软件重置初始化设备

{0x04,0x03},// 2。 将PLL_CLKIN设置为MCLK,将CODEC _CLKIN设置为PLL_CLK

{0x05,0x93},// 3. 打开PLL电源,设置PLL分配器P=1和PLL分配器R=3

{0x06,0x07},// 4. 设置PLL分配器J=7

{0x07,0x00},// 5. 设置PLL分配器D=0000

{0x08,0x00},// 6。

{0x0B,0x83},// 7。 开机并设置NDAC分配器= 3

{0x0c,0x87},// 8。 开机并设置MDAC分配器=7

{0x0d,0x00},// 9。 设置DOSR = 128 MSB //for32Khz

{0x0E,0x80},//10。 设置DOSR = 128 LSB //for32Khz

{0x1b,0x3c},//11。 设置I2S接口,字长32位,BCLK输出,WCLK输出

{0x3c,0x11},//12。 DAC模式至PRB_P17

{0x1d,0x05},//13。 BDIV_CLKIN = DAC_MOD_CLK

{0x1E,0x82},//14。 接通电源并设置BCLK N分配器= 2 //对于32KHz

{0x00,0x01},//15。 选择第1页

{0x01,0x08},//16。 在存在外部AVdd供应的情况下禁用内部原油AVdd

{0x02,0x00},//17。 启用主模拟电源控制

{0x7B,0x01},//18。 将参考充电时间设置为40ms

{0x0a,0x00},//19。 将输入共模设置为0.9V,并将耳机的输出共模设置为输入共模

{0x0c,0x08},//20。 将左侧DAC和INL路由至HPL

{0x0d,0x08},//21。 将右侧DAC和INR路由至HPR

{0x03,0x00},//22。 将DAC PTM模式设置为PTM_P3

{0x04,0x00},//23。

{0x10,0x00},//24。 将HPL增益设置为0dB

{0x11,0x00},//25。 将HPR增益设置为0dB

{0x14,0x29},//26。 HP软步进设置可在开机时获得最佳的PoP性能。 使用的RPOP为6k,N = 6,软步进= 20usec

{0x09,0x30},//27。 启动HPL和HPR驱动程序

//#----------- 等待2.5 sec,软步进才能生效

//#----------- 另请阅读第1页,注册63d,D (7:6)。 当=“11”软步进完成时

{0x00,0x00},// 28。 选择第0页

{0x44,0x00},//29。 DRC控制寄存器1,禁用DRC

{0x3f,0xd6},//30。 打开左侧和右侧DAC通道的电源,并路由左侧通道I2S数据

//到左通道DAC和右通道I2S数据到右通道DAC

{0x40,0x00}//31。 取消DAC数字音量控制的静音

谢谢。

Y.W. 风扇