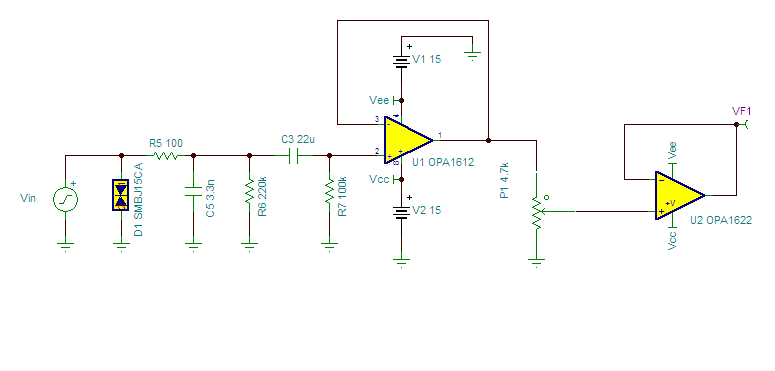

主题中讨论的其他部件:OPA1622, TINA-TI, LME4.96万, OPA1644, OPA1612, OPA1602

尊敬的TI comunnity,您好!

我从TI主站点获得了一些有关TIDU034设计的问题。

这些问题(我的问题)或多或少与共模失真有关,并降低了该电路的易受害性?

如果共模失真是由于IN-和IN+上的阻抗不匹配导致的,那么我们需要在U1A阶段使其相等吗?

我们知道输入级的值,假设DAC输出电阻器为50-100R。

根据AD743 PDF,我们需要:

这是否正确,或者在音频带失真方面根本不重要?

另一个问题是,我们能否降低R10 22K电阻? OPA160x或164x都是非常低的输入偏置电流,因此我认为我可以放置较低的电阻器,它也可以改善噪声,甚至可以将其去除?

如何将相同值的电阻器置于U1C的反馈路径中? 电路使用典型的单位增益缓冲器,但在输入和输出之间添加一个电阻器并不是一个不可避免的问题。

另一个问题是U1D级的输出阻抗? 它是固定的还是因电位计的锥形位置而变化的?

这一点非常重要,因为如果我在非反相模式下连接任何缓冲区,它将或多或少地受到共模失真的影响我对吗?

如果输出阻抗是可变的,我是否应该移动U1B反相级和缓冲U1D输出? 由于U1B的反相特性,我的相位将与输入相同,我的输出缓冲器(即OPA1622作为单位增益缓冲器)不会出现共模失真。

我是否对这些都正确,或者我是否应该找到其他解决方案来使一切都正确?

如果我是对的,那么我可以在没有额外的小部件或几乎不需要任何费用的情况下进行一些性能升级-这将是很好的,更好的。

我有最后一个问题,它与OPA1622有关,ATM我将它用作任何全局反馈环路之外的独立缓冲区。

我是否应该使用OPA160x或OPA164x反馈回路将OPA1622包含在其中?

如果是,为什么? 如果不是,原因是什么?

我阅读了一些关于复合运算放大器级的文档,但它更多地与CFB运算放大器或运算放大器有关,这些运算放大器实际上是高输入偏置电流/直流偏移等

感谢您的参与,祝您度过美好的一天:)