您好,

我正在尝试使FS 16kHz,SCLK = 32*FS,MCLK = 256*FS模式工作,这是数据表中单速软件控制模式所允许的。

理想情况下,这需要4.096 MHz MCLK,但我的MCLK源仅为纯4.0 MHz (以及由此衍生的所有其他时钟),

这意味着2.3 % 低于理想值,尽管数据表中没有提到频率容差。

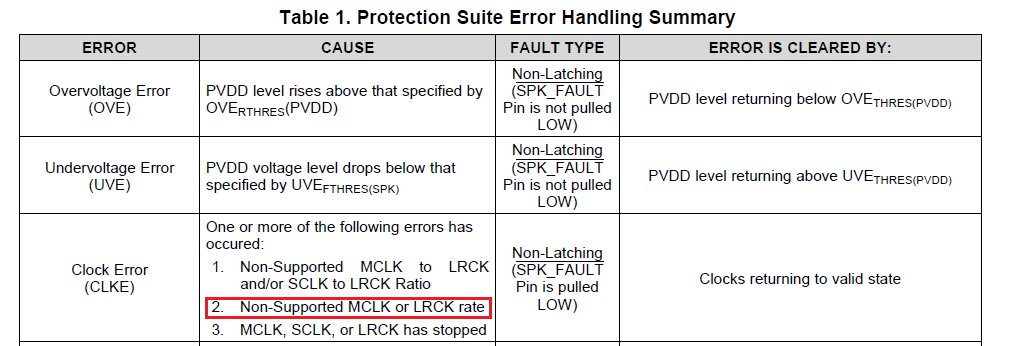

该部件一直给我一个稳定的CLKE错误(寄存器8中的第3位),它应该是非锁定的,

因此,这意味着错误无法恢复。

我尝试在时钟已打开后重新切换/SPK_SD并重新编程寄存器,但这没有帮助。

(可能不相关的信息:虽然该部件仅驱动一个扬声器,但在两个I2S通道中都有相同的16位I2S数据,

我尝试过,但尝试过BTL和PBTL设置,但没有变化)。