您好,

TLV320ADC3101 支持I2S的TDM + DSP多通道配置。

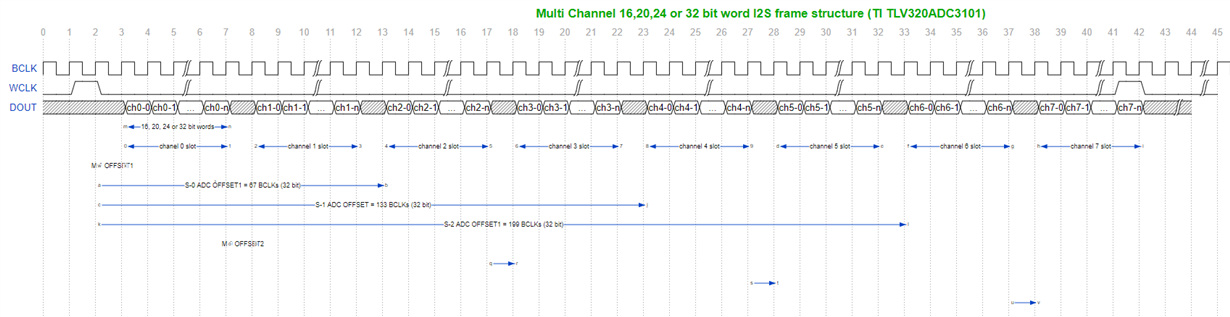

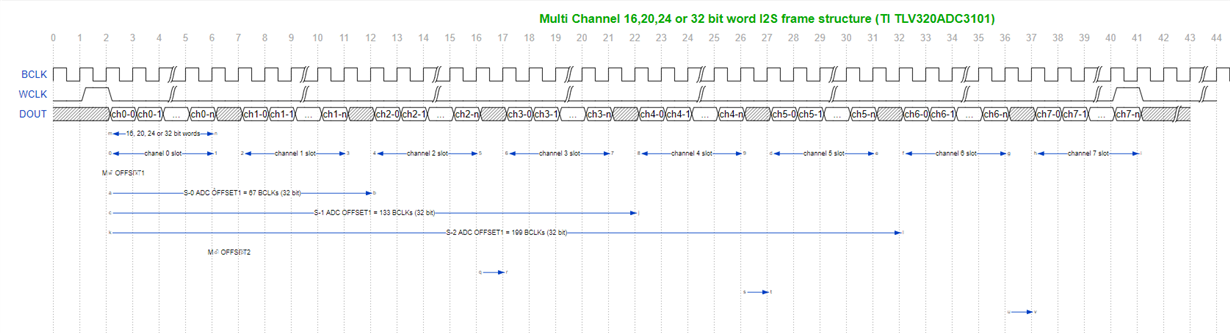

通过在i2c上连接4个ADC (1个主适配器,3个从适配器)并按如下方式对各种寄存器进行编程(ADC音频接口控制,I2S tdm控制,数据插槽偏移1,数据插槽偏移2),预期的I2S帧结构应类似于以下内容:

是否有ADC模型可用于根据给定配置(在系统Verilog或C中)生成预期I2S输出?

我有4个ADC的配置,应该会产生上述输出,但如果可能,我想根据 TLV320ADC3101部件的型号验证该配置。

如果有任何帮助,我们将不胜感激。

谢谢!

Cian