主题: TLV320AIC33中讨论的其它部件

您好,

我在Telit LE910模块和AIC3104编解码器之间遇到有关I2S的通信问题。

i2c配置接口,也是LINE1LP到LEFT_LOP的环回配置,工作正常。

我的目标是从LINE1LP到I2S-Interface,以及从I2S-Interface到LEFT_LOP单端读取单声道信号。

LE910-Master的I2S配置为:

模式:TDM

BCLK:4096 kHz

采样率:16 kHz

WCLK:16 kHz高脉冲,用于1个BCLK时钟,每帧256个时钟。

每样本位数:16

信号电平为1.8V

我 尝试了以下配置

#!/bin/bash

# I2C-Busse suchen

modprobe i2c-dev

#寄存器1:软件重置寄存器

i2cset -y 7 0x18 0x01 0x80

睡眠1

#寄存器102:时钟生成控制寄存器:CLKDIV_In使用BCLK,PLLCLK _In使用BCLK

i2cset -y 7 0x18 0x66 0x62

#########################################################################################################################################################################################################################################################

#高速模式:BCLK * 1 => J=24,D=0,R=1,P=1 (从4096kHz BCLK生成1.2288万 kHz内部时钟,fsref=48kHz,FS=16kHz)

# Page 0/Register 2:编解码器采样率选择寄存器(Sample-rate FS=fsref/3)

i2cset -y 7 0x18 0x02 0x44

#第0页/注册3:PLL编程寄存器A (PLL启用,P=1,Q=16)

i2cset -y 7 0x18 0x03 0x81

#第0页/寄存器4:PLL编程寄存器B (J=24)

i2cset -y 7 0x18 0x04 0x60

#第0页/寄存器5:PLL编程寄存器C (D=0)

i2cset -y 7 0x18 0x05 0x00

#第0页/寄存器6:PLL编程寄存器D (D=0)

i2cset -y 7 0x18 0x06 0x00

#第0页/注册11:PLL编程(R=1)

i2cset -y 7 0x18 0x0B 0x01

# Page 0/Register 9:音频串行数据接口控制寄存器B DSP-模式,256位,ADC-,DAC- Resync)

i2cset -y 7 0x18 0x09 0x4E

#########################################################################################################################################################################################################################################################

#第0/Register 19页:MIC1LP/LINE1LP到左ADC控制寄存器

i2cset -y 7 0x18 0x13 0x04

# Page 0/寄存器15:左ADC PGA增益控制寄存器(取消静音左PGA,将增益设置为0 dB)

i2cset -y 7 0x18 0x0F 0x00

# Page 0/注册7:编解码器数据路径设置寄存器(将左侧数据路由至左侧DAC)

i2cset -y 7 0x18 0x07 0x08

# Page 0/Register 37:DAC电源和输出驱动器控制寄存器(加电左DAC)

#? HPLCOM是否配置为独立单端输出? 0xA0

i2cset -y 7 0x18 0x25 0x80

# Page 0/Register 41: DAC Output Switching Control Register (左DAC输出选择DAC_L1路径至左线路输出驱动器)。

i2cset -y 7 0x18 0x29 0x00

# Page 0/寄存器43:左DAC数字音量控制(取消左数字音量控制静音,将增益设置为0 dB)

i2cset -y 7 0x18 0x2B 0x00

# Page 0/Register 82:DAC_L1至LEFT LOP/M音量控制寄存器(将左DAC输出路由至左侧线路输出)

i2cset -y 7 0x18 0x52 0x80

# Page 0/Register 86: LEFT输出电平控制寄存器(0dB增益左线路输出,LEFT LOP通电)

i2cset -y 7 0x18 0x56 0x09

结果是,我既没有从输入中获取样品,也没有从左侧_LOP的DIN中找到样品。

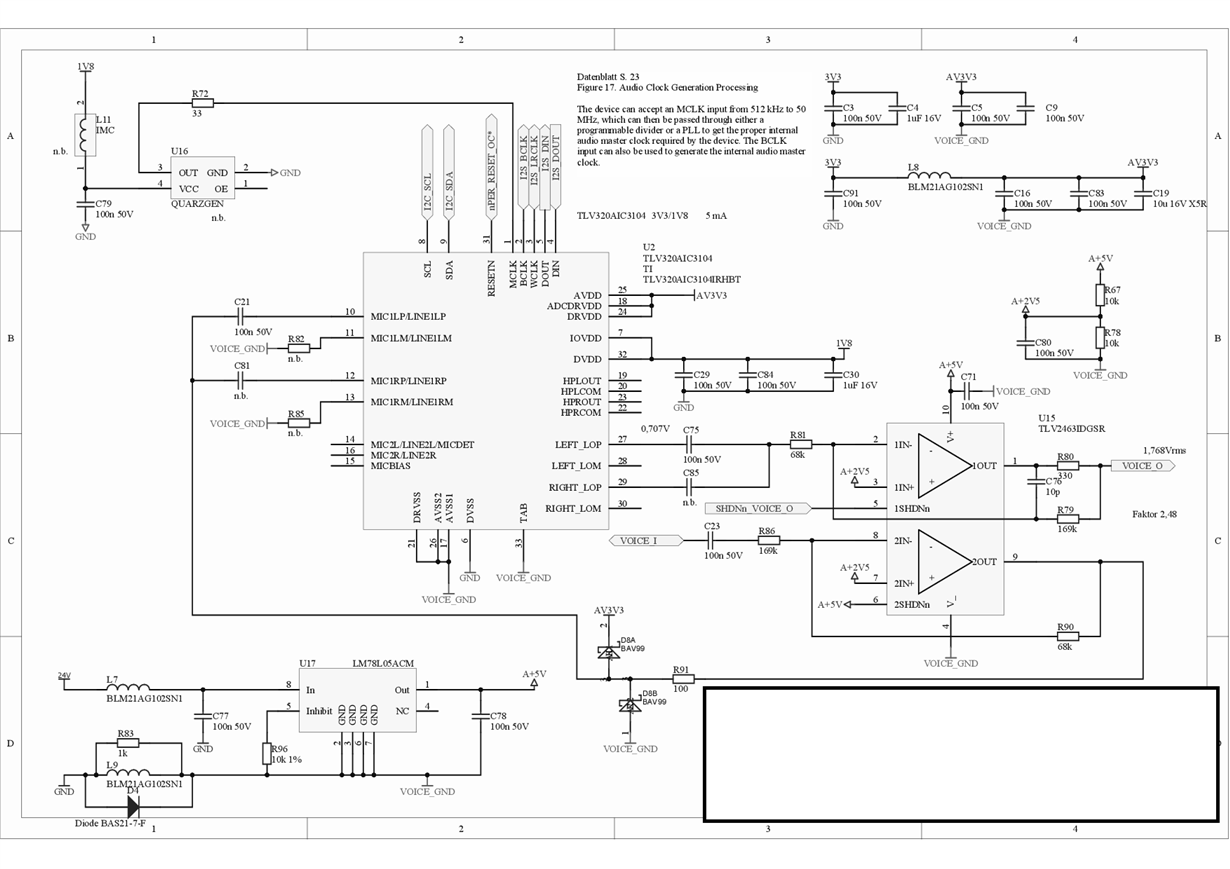

编解码器的示意图:

我的配置有什么问题?

此致

格雷戈