请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:DIX4192-Q1 主题中讨论的其他部件:DIX4192

BLS和SYNC的反弹是什么?

如何在系统中使用BLS和SYNC?

请举例说明BLS和SYNC的实用程序。

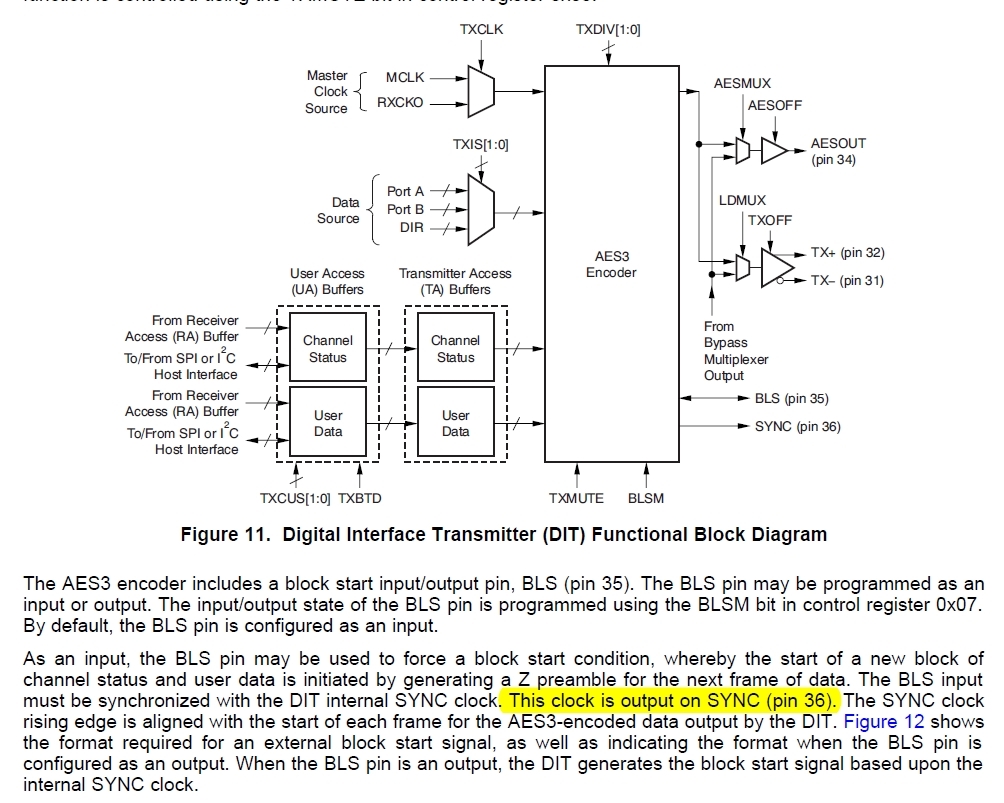

DIX4192应用于我们的系统,将I2S数据传输至SPDIF (AES编码数据)。

线路驱动器输出与CMOS缓冲输出到DIT外部逻辑之间有何区别? 线路驱动器是否用于驱动长电缆(远端)  和用于驱动电路(近端)的CMOS缓冲器?

和用于驱动电路(近端)的CMOS缓冲器?