https://e2e.ti.com/support/audio-group/audio/f/audio-forum/688991/pcm1802-noise-from-pcm1802

部件号:PCM1802主题中讨论的其他部件:PCM1792A,

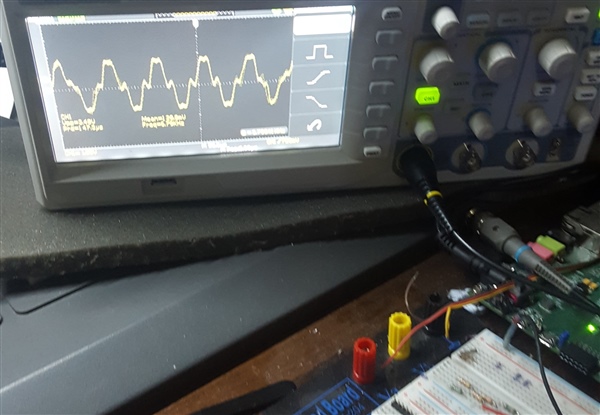

我可能做错了事,但我已经使用我的VHDL代码完成了所有的模拟,我知道我的DAC正在工作(PCM1792a),因为我能够从FPGA生成和输出锯齿波。 当通过PCM1802将正弦波,三角波或锯齿波传递到FPGA并输出到PCM1792A时,输出信号非常嘈杂。 它随着频率的提高而有所改善,但会出现闪烁和不希望听到的噪音。 我的时钟很好,我把所有东西都建立在串行块的基础上,并为此计时。

我的ADC接收器代码如下:

库IEEE; 使用IEEE-STD_LOGIC_1164.ALL; 使用IEEE-std_logic_arith; 使用IEEE-std_logic_unsigned; 使用IEEE-numeric_std.all; 实体I2SRX为 端口( CLK :在STD_LOGIC;中 CL:在STD_LOGIC中; DIN:在STD_LOGIC中; LD:输出STD_LOGIC_Vector (23下降到0); Rd:输出STD_LOGIC_Vector (23下降到0); FCK:输出STD_LOGIC; SCK:输出STD_LOGIC; BCK:输出STD_LOGIC; LRCK:OUT STD_LOGIC); END I2SRX; I2SRX的体系结构行为是 信号CLKDIV:整数范围0至260; 信号CLKDIV 2:整数范围0至1万:= 0; 信号CNTR:整数范围0至24:= 23; 信号CNTR2:整数范围0至50; 信号CNTR3: 整数范围0到4:= 0; 信号d1 :std_logic_vector(23 downto 0); 信号d2. :std_logic_vector(23 downto 0); 信号D1P :std_logic_vector(23 downto 0); 信号D2P : std_logic_vector(23 downto 0); signal BUF : std_logic; 信号CLK1 : std_logic :='0'; 信号CLK2 : std_logic :='0'; 信号FME : std_logic :='0'; begin --BLCK生成 过程(clk, cl) 开始 如果(CL'event and CL ='0'),则 -- buf <= DIN; 如果(CLKDIV2 = 1),则 CLKDIV2 <= 0; CLK2 <=不是CLK2; 否则 CLKDIV2 <= CLKDIV2 + 1; 结束条件: 如果(CNTR3 = 3),则 CNTR3 <= 0; 否则 CNTR3 <= CNTR3 +1; 结束条件: 结束条件: --bck <= CLK2; 结束进程; 进程(FME) 开始 如果(FME'事件和FME ='0'),则 如果(CLK1 ='0'),则 D1P <= D1; 否则 D2P <= D2; 结束条件: END IF; END PROCESS; --左时钟生成 过程(clk,CLK2) 开始 如果(CLK2'事件和CLK2 ='0'),则 如果(CLKDIV =31),则--was 31 CLKDIV <= 0; CLK1 <=不是CLK1; --LD <= d1; -RD <= D2; 否则 CLKDIV <= CLKDIV + 1; 结束条件: END IF; END PROCESS; --PROCESS (CLK) --BEGIN -- SCK <=CL; -- IF (CNTR3 = 3)那么 -- BUF <= DIN; -- END IF; -- END PROCESS; PROCESS (CLK,CLK2) BEGIN 如果(CLK2'事件和CLK2 ='0'),则 如果(CNTR <= 23),则 如果(CNTR /= 0),则 CNTR <= CNTR -1; 否则 FME <='0'; 如果(CLKDIV = 0),则 CNTR <=23; FME <='1'; 结束条件: 结束条件: 结束条件: 结束条件: 如果(CNTR <= 23),则 如果(FME ='1'),则 如果(CLK1 ='0'),则 D1 (CNTR)<= DIN; 否则 D2 (CNTR)<= DIN; 结束条件: 结束条件: END IF; -- Bck <= CLK2; END PROCESS; LD <= D1P; RD <= D2P; BUF <= DIN; LRCK <= CLK1; Bck <= CLK2; FCK <= FME; 端部行为;