请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/707676/dix4192-datasheet-diagram

部件号:DIX4192您好,

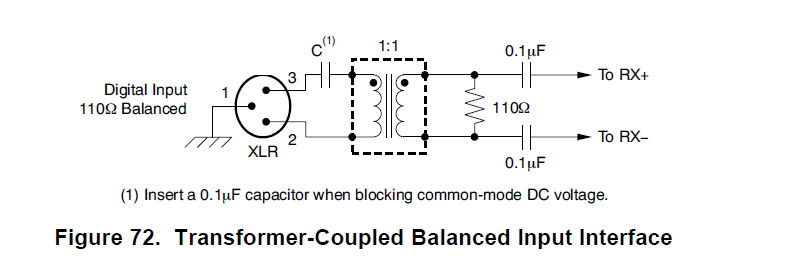

当使用DIX4192进行新的电路板布局时,注意到数据表图72显示XLR连接(引脚3为正相连接)。 这与此类平衡连接(即引脚3负极和引脚2正极)的指定值相反

以这种方式连接是否有任何问题?