https://e2e.ti.com/support/audio-group/audio/f/audio-forum/736780/lm5141-q1-ic-is-too-hot

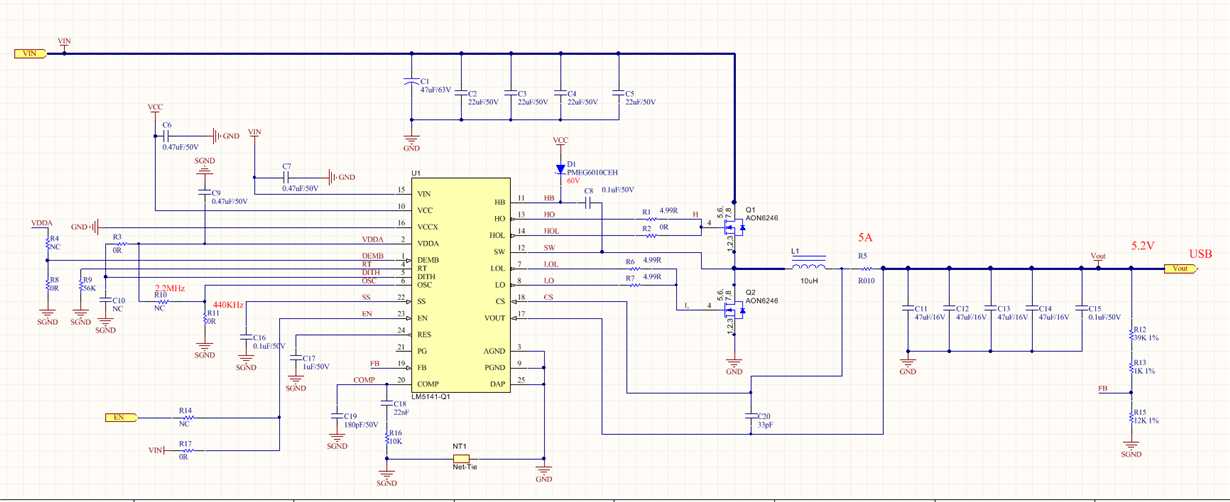

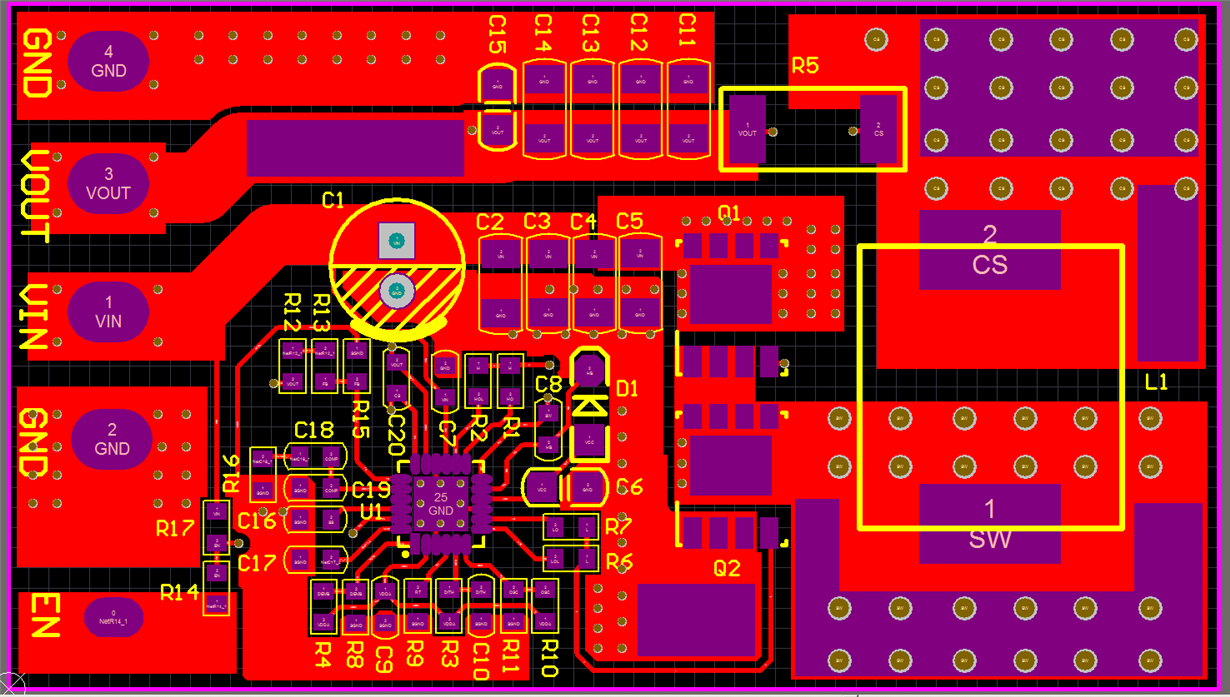

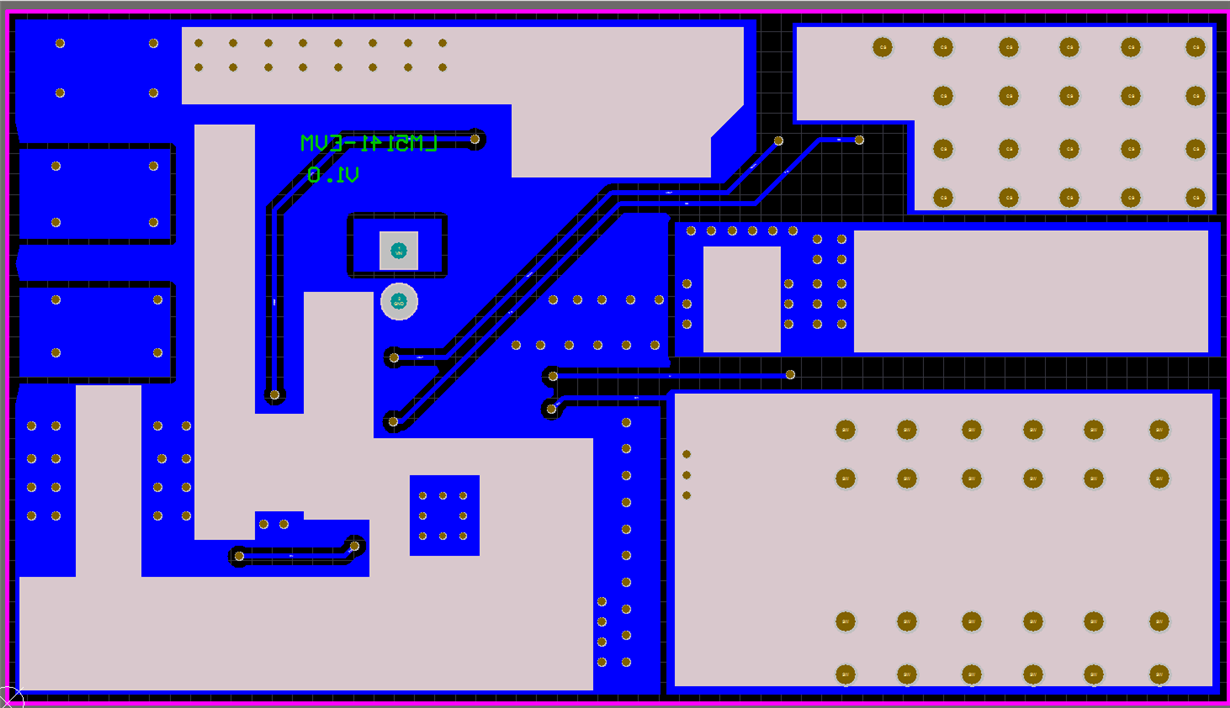

在“线程:LM5141”中讨论的其他部件这是我的第二个设计LM5141,40V-5.2V DC-DC

我设计EVM时参考 了WENBENCH工具原理图

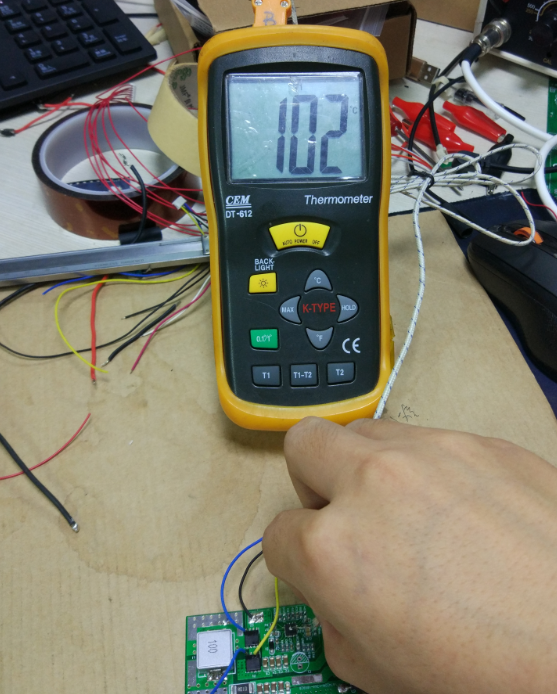

当输入为40V,时,输出为5.V 3A,IC,MOS极热,约100℃,

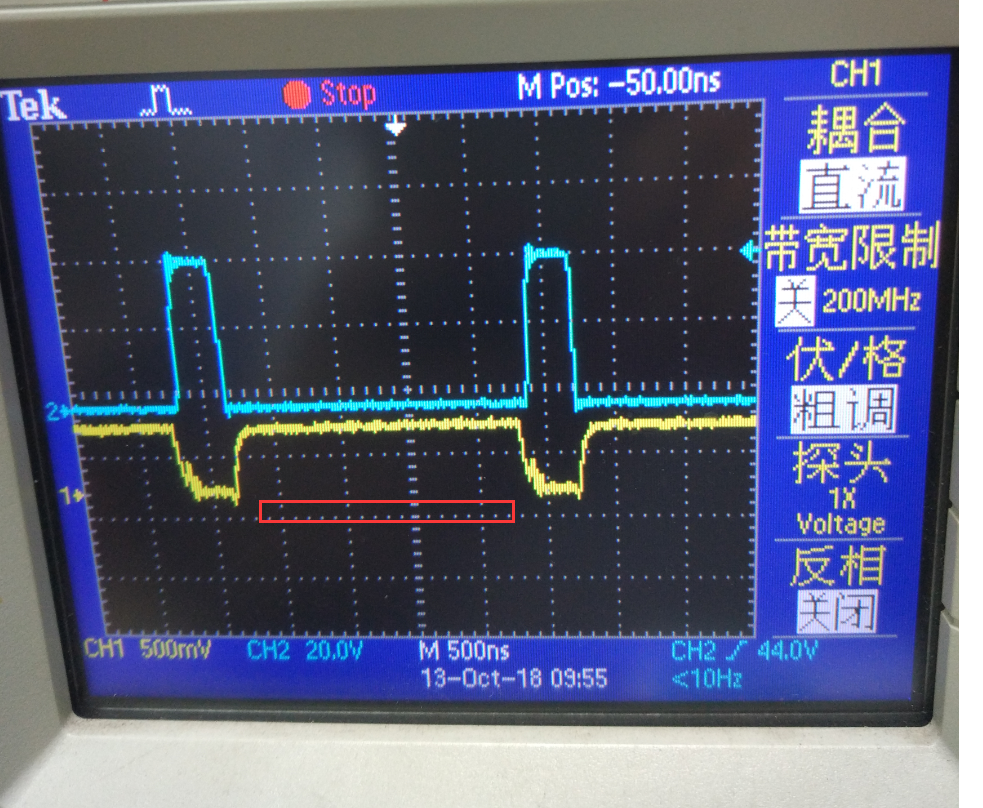

下面是有关不同输出电流,。的高低MOS驱动器波形的图片

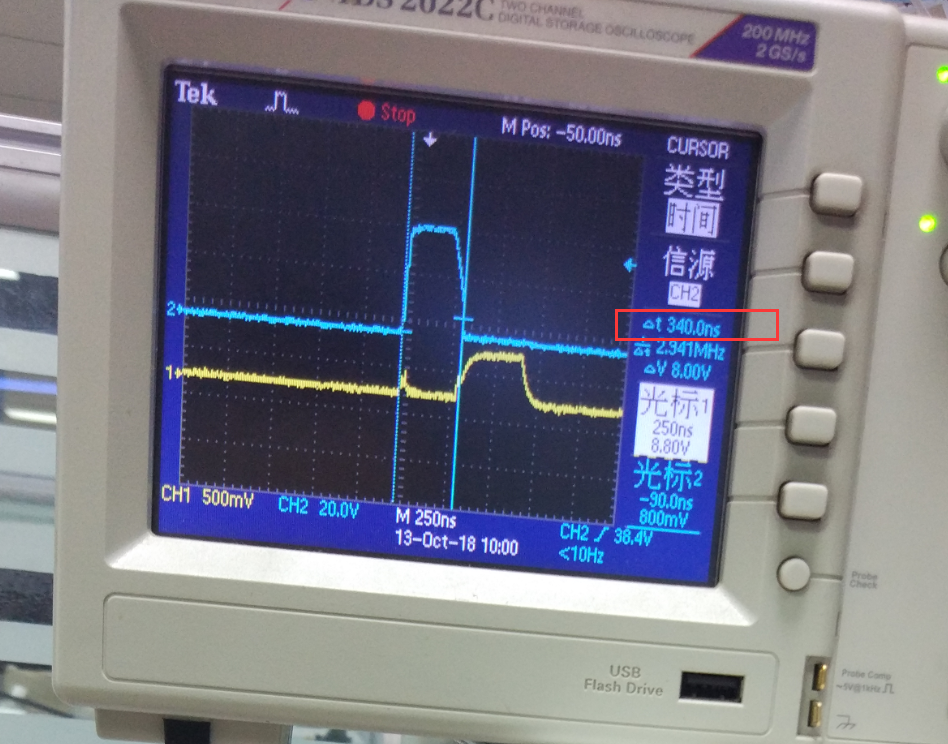

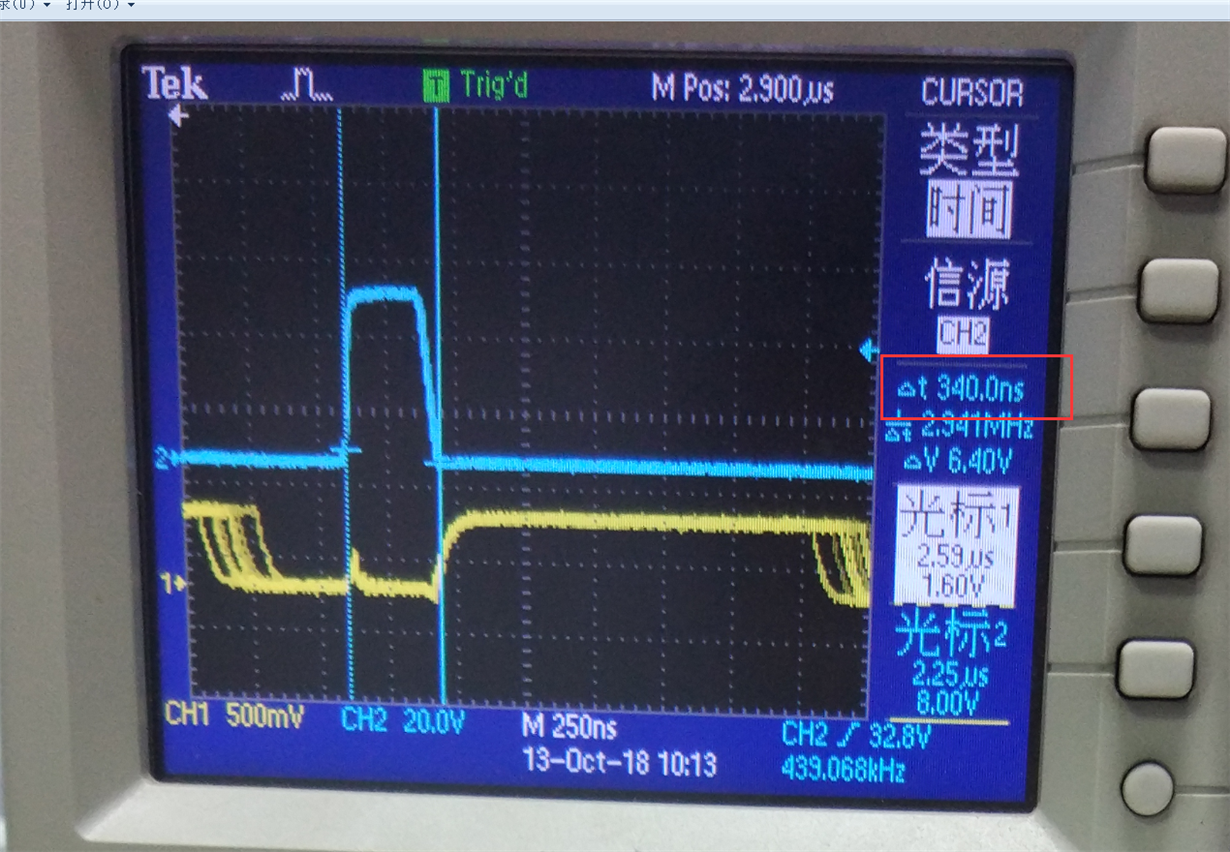

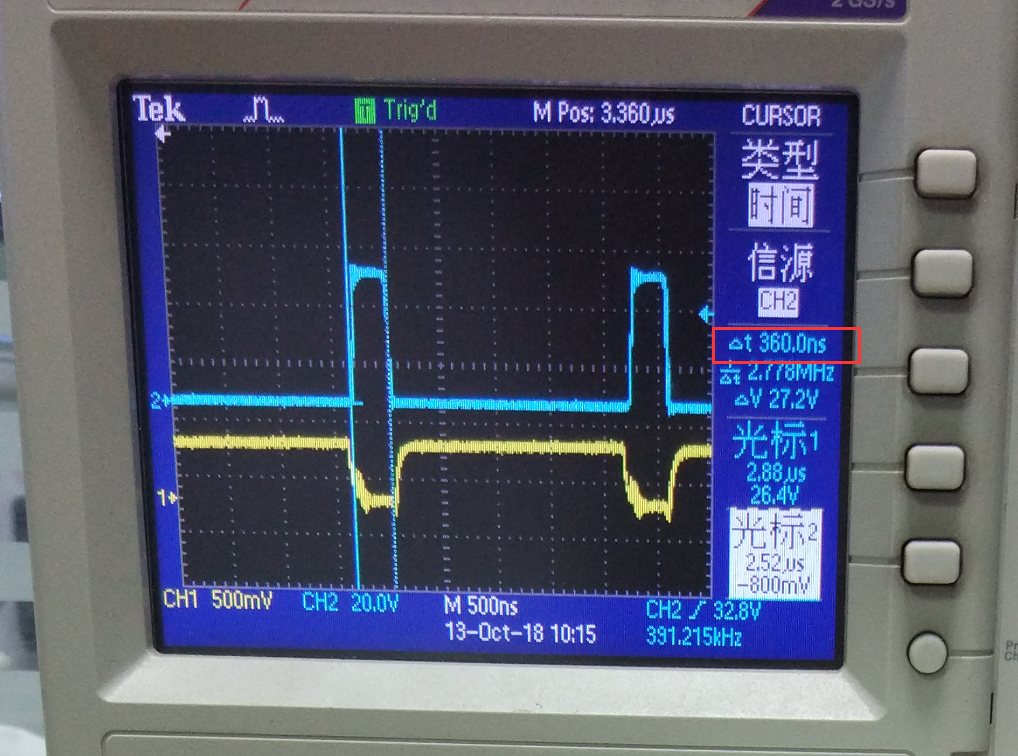

蓝色图是高MOS驱动器

黄色图为低MOS驱动器

输出is1A

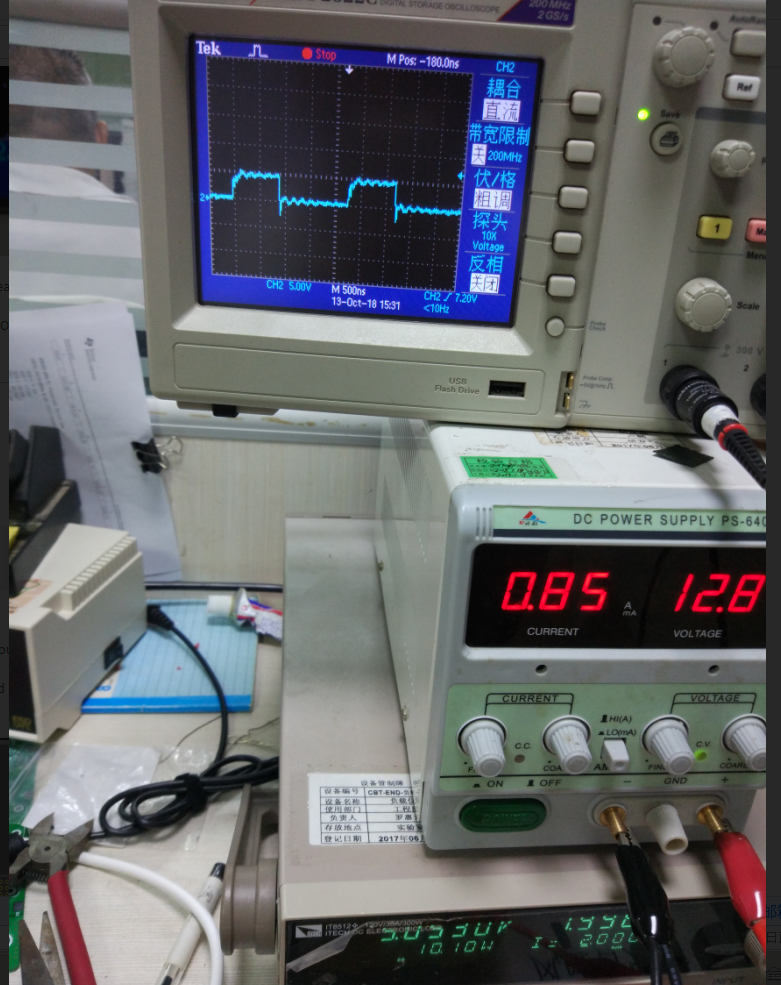

输出为2A

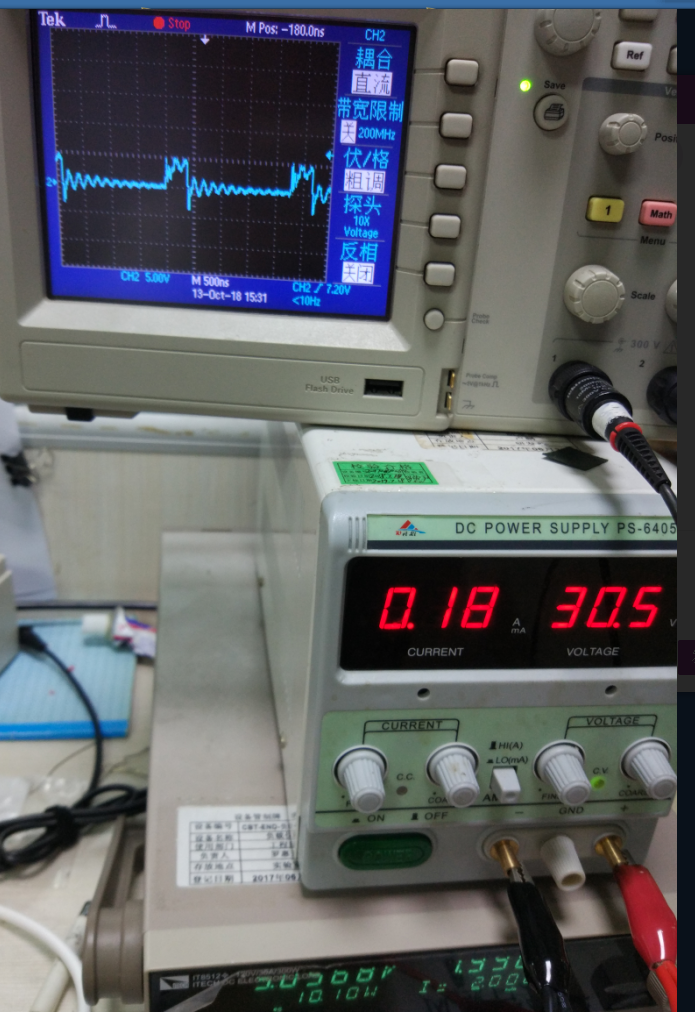

输出为3A

参见上图,当操作不同的输出电流 时,高MOSFET驱动器打开时间几乎保持不变

让我们来看看 不同输出电流下的低MOS潜水员波变化

1a.

2a.

3a.

我正在询问,像往常一样,当加载时,高驱动器应该获得降压电路中的占空比,否则 这种状态 不是我的希望,为什么 当 输出电流 增加1A 到3A时只增加了低驱动器占空比?

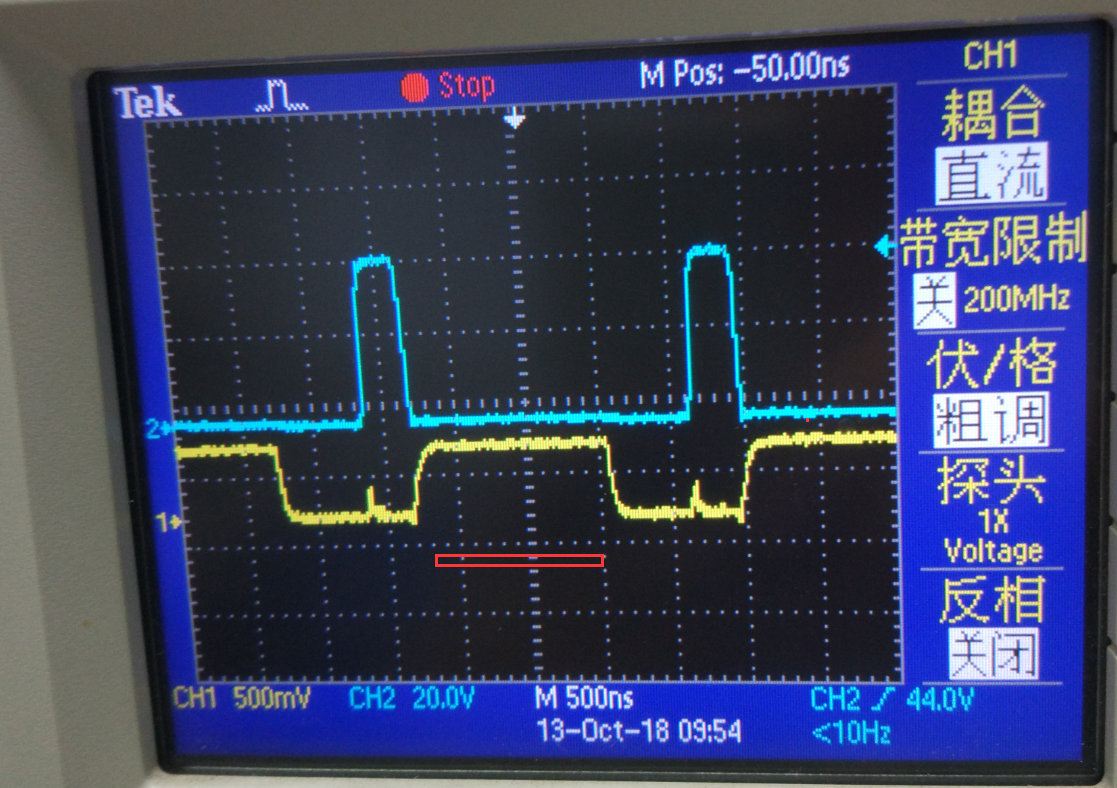

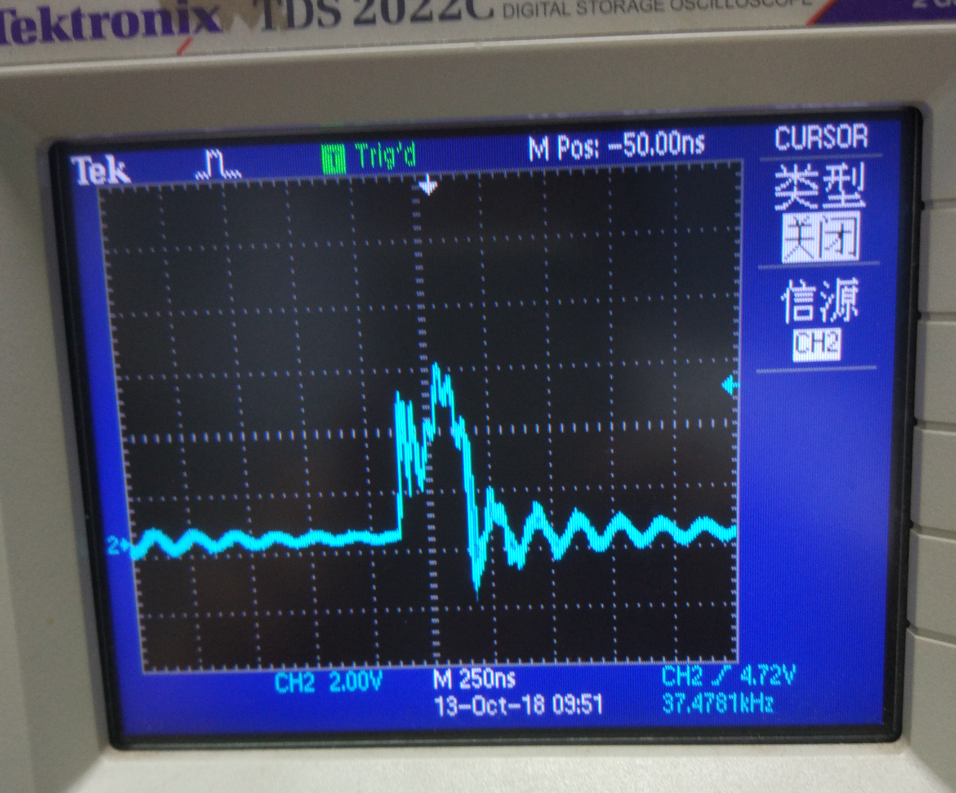

我测试 了高MOS Vgs,波形非常奇怪

它看起来不像完整工作,如果这是MOSFET温度很高的原因,即使输出只有1A,也是如此

所以我的主要问题是IC和 MOSFET的情况,我希望有人能帮助我解决这个问题