各位专家:

当我测试 TLV320ADC5120 EVM 时、发现左通道和右通道之间的 THD+N 存在较大的间隙。 我不明白为什么需要您的支持来解决此问题。

测试设置:

电源:AVDD=IOVDD=1.8V。

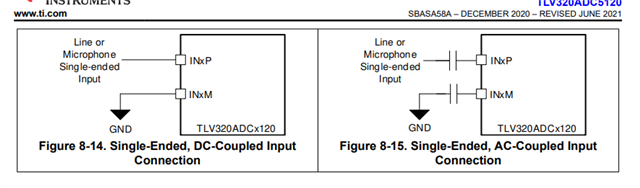

输入设置:单端(1N 和2N 负输入引脚连接至接地)Ω、输入500mVrms 1kHz 正弦波。

PPC3设置:单端、线路输入、10kΩ Ω 输入阻抗、增益=odb、32位 I2S 从器件输出。

AP 输入时钟为 I2S 256fs fs=48K。 以 dB 为单位测试 THD+N。

测试结果如下所示:

| THD+N |

| 左通道-88.3dB/RIGHT 通道-68.1dB (DRE ON、2.5K、0dB 增益、500mV 输入) |

| 左通道-87.8dB/右通道-72.7dB (DRE 打开、10K、0dB 增益、500mV 输入) |

| 左通道-87.6dB/右通道-72.5dB (DRE 关闭、10K、0dB 增益、500mV 输入) |

第2项测试未更改任何设置、只是将电源更改为 AVDD=IOVDD=3.3V。左右通道 THD+N 看起来正常。

| AVDD=IOVDD=3.3V |

| 左通道 -92.3dB/右通道-91.2dB (DRE ON、10K、0dB 增益、500mV 输入) |

谢谢。

Anderson