https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1112914/supported-sample-frequencies

器件型号:PCM1865我们将在从器件时钟模式下使用不带 SCK 的 PCM1865。

我们的目标采样频率将是52.1kHz 的倍数。 这超出了表11 (第9.3.9.4.4章 BCK 输入从机 PLL 模式)列出的专用采样频率、也超出了数据表(32..48kHz、88.2..96kHz、176,4..192kHz)中地址0x73 (第0页)寄存器显示的采样频率范围。

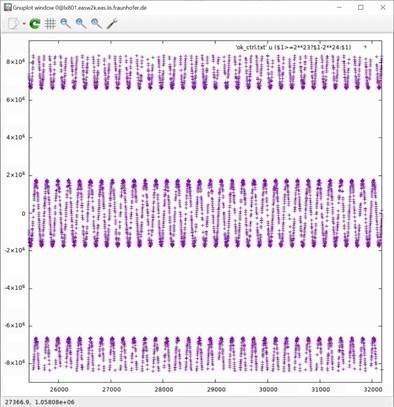

我们尝试使用48 (LRCK=52、1kHz、BCK=2、5MHz)的 BCK 比率和64 (LRCK=52、1kHz、BCK=3、334MHz)的 BCK 比率。 两者都没有成功(I2S 输出上有足够的采样值)。 PCM1865是否可以使用此设置?

非常感谢+此致。