Other Parts Discussed in Thread: PCM1862

专家您好!

我对 PCM1862的内部 PGA 有疑问。

您会回答以下问题吗?

1.您是否会根据配置步骤(0.5dB)提供 PGA 增益误差的最小/最大数据?(例如、它是0.5dB+-0.2dB)

2.当我们将 PGA 增益配置为导致饱和时、是否存在除输出数据 spatulation 之外的任何问题?(例如、将2.1Vrms 输入的增益配置为+32dB)

3.当我们在 不停止 I2S 的情况下更改 I2S BCLK 的频率时、是否存在对器件造成损坏的类似风险?

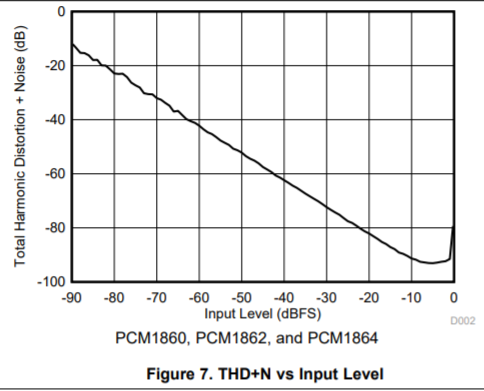

我们预计可以将音频输入信号转换为0dB、但我们观察到、在特定条件下、音频数据失真约为-2dB、如下所示。 您是否会告诉我以下行为是否符合预期?

我们将通道配置为差分和15.5dB、并输入小于2.1V 的模拟音频信号。 然后、我们期望我们可以观察到信号不失真、直到数字音频输出达到0dB。 但是。 数字音频数据 的失真范围为-2.1dB。

我很期待收到您的回复。

此致、

Kazuki Kuramochi