Other Parts Discussed in Thread: PCM3008

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1018886/pcm3008-reference-of-do-timing

器件型号:PCM3008大家好、

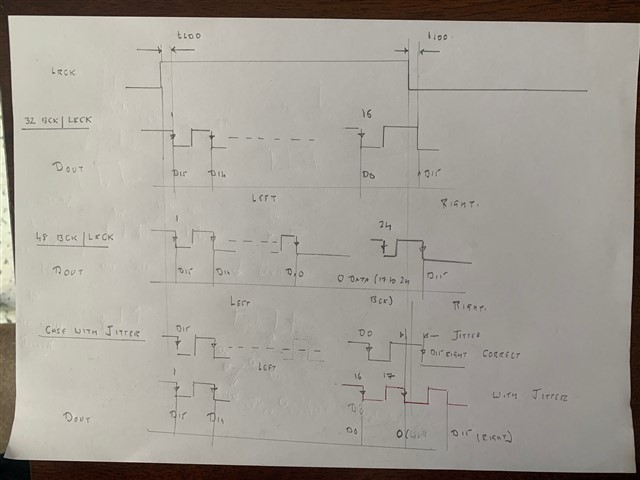

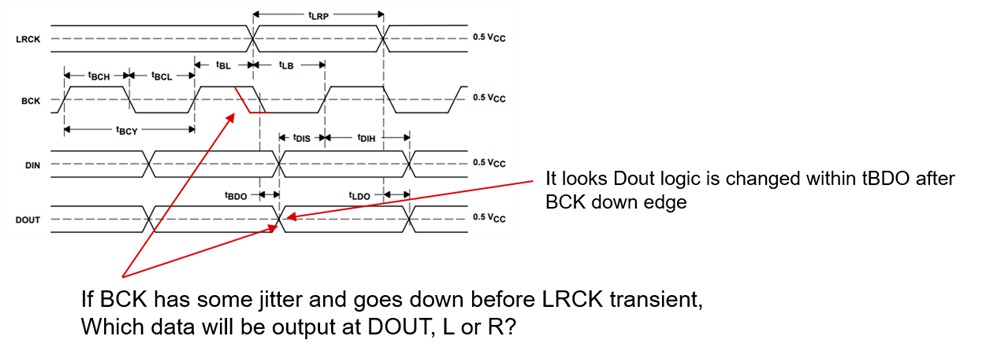

您能告诉我哪个时钟执行输出时序基于 LRCK 或 BCK 吗?

BCK 时钟在我的客户系统中有一些抖动、有时它在 LRCK 下降沿之前下降。 它们选择左对齐模式、因此它们希望确认当 BCK 在 LRCK 下沿之前下降时如何处理第一个位数据。

此致、

Takashi Onawa