https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1026225/tlv320aic3204-capacitive-load

器件型号:TLV320AIC3204团队、

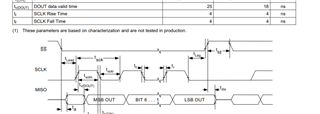

我正在使用 TI TLV320AIC3204IRHBT 编解码器进行设计,我的方案是,在同一 SPI 总线上有6个编解码器,并将 FPGA 用作总线主控。 我正在尝试了解编解码器施加的电容负载类型以及可以在其数字 IO 上驱动的电容负载。 它们看起来具有10pF 的输入电容,但不清楚它们在10MHz SPI 总线上能够可靠驱动的是什么:

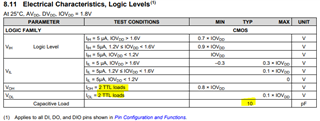

“2 TTL 负载”是测试条件。 在我的案例中、MISO 线路上有6个编解码器(每个10pF)和 FPGA (4pF)、因此总共~64pF。 将上述数据表解释为表示编解码器 IO 可以驱动20pF 是否错误?

感谢您提供有关此器件的更多信息。