您好的团队:

我们使用 TLV320AIC3104 在 RY_LOM/LOP 上输出稳定的声音信号。 现在、Rright_LOP 具有声音输出、而 Rright_LOM 没有声音输出。 我遵循以下文档说明:

寄存器89和寄存器92的1.D7被路由至 DAC_L1/R1立体声通道至 Rright_LOP/LOM。 默认情况下、寄存器92的 D7设置为1。

2.寄存器89设置为1,Rright_LOM 仍然没有声音。

是否有需要注意的寄存器? Tks 为您提供支持!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好的团队:

我们使用 TLV320AIC3104 在 RY_LOM/LOP 上输出稳定的声音信号。 现在、Rright_LOP 具有声音输出、而 Rright_LOM 没有声音输出。 我遵循以下文档说明:

寄存器89和寄存器92的1.D7被路由至 DAC_L1/R1立体声通道至 Rright_LOP/LOM。 默认情况下、寄存器92的 D7设置为1。

2.寄存器89设置为1,Rright_LOM 仍然没有声音。

是否有需要注意的寄存器? Tks 为您提供支持!

您好!

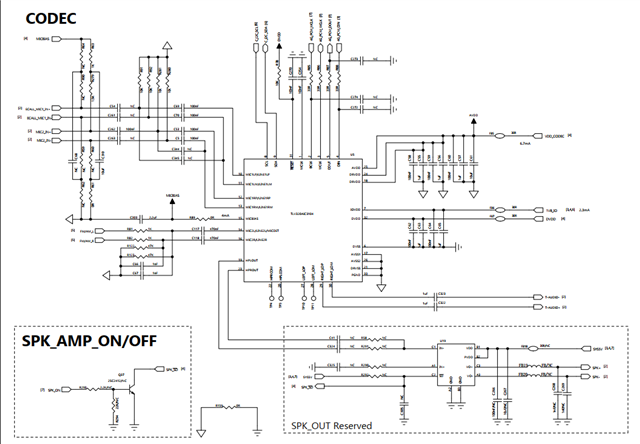

我建议使用数据表中的图10-2作为参考、我在这里将其与您的设置一起显示。

您实际上是将 DAC 左侧和 DAC 右侧混合到右侧线路差分输出中。

我建议将此图与寄存器映射一起使用、以根据您的需要配置器件。 括号中的字符是十进制的寄存器地址、例如(R89)用于寄存器89。 我不知道您的寄存器中还设置了什么、但正确的线路输出是差动输出(R93)、因此两者都应该输出。

尝试使用上述方法配置器件、如果器件仍然无法正常工作、则向我发送寄存器设置。

此致。

您好 、pdjuandi:

Tks 供您发表评论。 只需与客户核实、所有电路板上都会出现此问题。

我附加了如下寄存器、希望您看一下。 太棒了!

他们的寄存器设置不正确、我已根据上面显示的路径添加了注释和建议。

现在、他们还需要检查一些内容、因为这是他们的主机提供的、以匹配此编解码器中配置的内容。

e2e.ti.com/.../4426.AIC3104-config-list.xlsx

此致。

这是16KHz DAC FS 设置。

e2e.ti.com/.../5618.AIC3104-config-list.xlsx

此致。

您好 、pdjuandi:

TKS 为了您的支持、您的配置文件在客户电路板上运行良好。

但用于进一步测试。 客户希望将音量输出 Vpp 设置为1.2V、但当我们将 DAC vol 设置为0x7f 时、只需获取300mV、

如我所见,127gain ->DAC 0x7f。 =>300mV

另一项测试是63增益-> DAC 0x33 => 50mV

我们是否有另一个寄存器可供进一步检查? 太棒了!

您是否在 Rright_LO 差分输出下获得了具有0dB RIGHT DAC 音量和0dB Rright_LO 输出电平的4Vpp?

我建议从顶部开始、确保您提供正确的输入并检查输出是否正确、为0dB。 然后、您可以开始降低 DAC 音量增益。

上述增益从0x7F 变为0x33毫无意义。 0x7f 将 信号降低63.5dB、0x33降低25.2dB、但数据显示了其他情况。

您好 、pdjuandi:

Tks 供您发表评论。 我们只需按照您的方法并进行修复。 但我们发现了 MIC 路径中的另一个问题。

在 B/D 下方、我们将 FM 信号连接到 MIC 引脚14、16。 您知道,FM 有时会有噪声,因此我们将 PGA 捕获音量更改为0,它可以 消除噪声,但有时我们发现 MIC 部件中没有声音。 这可能是由 PGA 设置引起的。

您是否会同意一些关于降低 FM 噪声的建议? Tks ~

您好 、pdjuandi:

TKS、以获取您的反馈。

[引用 userid="35889" URL"~/support/audio-group/audio/f/audio-forum/1126477/tlv320aic3104-right_lop-lom-output-issue/4195669 #4195669"]您是否在您的语句" FM 有时会产生噪声"中说输入源(FM)本身会产生噪声、并且您想消除噪声?是的、我们需要消除来自 FM 的噪声。 并在终端部件处具有更好的信号。

[引用 userid="35889" URL"~/support/audio-group/audio/f/audio-forum/1126477/tlv320aic3104-right_lop-lom-output-issue/4195669 #4195669"]当您说将卷更改为0时,您是指 将卷增益更改为0dB 还是没有卷(静音)?我们将 可编程增益放大器(PGA)更改为0dB、这是可行的。 但是、正常信号输出有时也会消失。

[引用 userid="35889" URL"~/support/audio-group/audio/f/audio-forum/1126477/tlv320aic3104-right_lop-lom-output-issue/4195669 #4195669"]没有音量或静音将导致没有输出,因此您不会听到任何声音,但0dB 增益意味着没有增益或衰减,但您将听到输入中的任何内容。明白了,客户似乎对 PGA 设置有一些误解,我们应该听到一切,没有 增益或衰减。

但是、除了增益设置之外、是否还需要一些常用的方法来降低噪声?

您好 、pdjuandi:

Tks 为了征求您的意见、以前更清楚了。

当我与客户核实 MCLK 的一些变化时、客户单独设置 BCLK。 基于 R102、我们尝试设置0xA2、但没有输出。

但0x82和0X22起作用、您能分享您的评论吗?

使用此时钟图、将 R102设置为0x82意味着您要将 CLKDIV_IN 设置为使用 BCLK、将 PLLCLK_IN 设置为使用 MCLK。

将其设置为0x22 意味着要将 CLKDIV_IN 设置为使用 MCLK 和 PLLCLK_IN 使用 BCLK、并将其设置为0xA2意味 着 CLKDIV_IN 和 PLLCLK_IN 都使用 BCLK。

因此、在您的用例中、您需要使用 PLL、并且由于您的 MCLK 物理连接到 BCLK、R102 D5-D4 00或10可以正常工作。

您是否修改了我发送的配置、或者它们是否相同? 您的0x82设置没有 PLL、并且噪声/回波是由于配置错误造成的。

您可能希望在示波器上捕获 MCLK/BCLK 和 WCLK、让我看看。

您好 、pdjuandi:

客户只对连接到 GND 的 MCLK 部件进行了一些修改。 我在下面添加了最新的寄存器列表和波形、您能帮助解决回波问题吗? Tks ~

您是否说它们将 MCLK 连接到 GND? 需要为编解码器提供 MCLK。

请检查您的寄存器、我建议现在只使用1条输出路径进行测试、即 HP 或线路、并使用相同的 DAC 路径。

我看到 DAC_L1连接到线路、DAC_R3连接到 HP。

另一个观察结果是您有1个时钟偏移、请交叉检查主机发送的内容、并确保其与示波器正确无误。

是、如下所示:

MCLK 通过100nF 连接到 GND。

我可以看到、客户认为他们可以将 R102设置为0xA2、因此 CLKDIV_IN 和 PLLCLK_IN 使用 BCLK 而不需要 MCLK、您是说不建议这样做吗?

此外、客户在呼叫时将 R102初始值设置为0x02、如果播放对讲机将设置 PCM 硬件接口、并将 R102设置为0xa2、您是否认为基于客户电路的 R102是可以的

您好 、pdjuandi:

[引用 userid="35889" URL"~/support/audio-group/audio/f/audio-forum/1126477/tlv320aic3104-right_lop-lom-output-issue/4202891 #4202891"]

请检查您的寄存器、我建议现在只使用1条输出路径进行测试、即 HP 或线路、并使用相同的 DAC 路径。

我看到 DAC_L1连接到线路、DAC_R3连接到 HP。

[/报价]正如您提到的这个主题、我让客户尝试设置 DAC L1与 DAC R1的相同路径、客户测试的结果如下:

将 DAC 切换至 DAC_R1/L1:

1.播放 FM 收音机,需要5-6秒才能输出声音。

2.要以呼叫者身份进行呼叫,请执行以下操作:

1)。 DAC_R1/L1的音量变得更小、并且不会从功率放大器中释放声音。

2)。 在拨打电话和播放 FM 收音机时、将从扬声器播放人声。

3)。 移动终端呼叫现在无法听到回声。

3.通话结束后挂断电话,您周围的人的声音仍将通过扬声器发出的小声音播放。

在 DAC_R1/L1的条件下、将 R10更改为0x00不会影响测试效果。

希望您能给我一些指导,tks~

你好 ,pdjuandi:

很抱歉给您带来不便、我想让您清楚地理解寄存器设置的逻辑。

[引用 userid="515753" URL"~/support/audio-group/audio/f/audio-forum/1126477/tlv320aic3104-right_lop-lom-output-issue/4205608 #4205608"]播放 FM 广播,需要5-6秒才能播放声音输出[/quot]关于此问题、FM 来自引脚14 16 (MIC2L/R)、输出来自引脚29 30 (Rright_LOM/P)。

因此、我认为我们应该使用 DAC_L1和 R1、 如图10-16中所述: 相反、如果 DAC 模拟输出必须同时路由到多个输出驱动器(例如 LEFT_LOP/M 和 Rright_LOP/M)或必须与其他模拟信号混合、则应通过 DAC_L1/R1路径切换 DAC 输出。

[引用 userid="35889" URL"~/support/audio-group/audio/f/audio-forum/1126477/tlv320aic3104-right_lop-lom-output-issue/4183754 #4183754"]5618.AIC3104配置列表.xlsx[/quot]但以您提供的先前配置列表为基础。 您可以将 R41设置为0X51、这意味 着 LEFT_DAC=DAC_L3、RIGHT _DAC=DAC_R3。 但我认为 LEFT_LOP/M 和 RIGHT _LOP/M 是单独的通道、用于输出 不同的音频信号。 您能帮助分享您的建议吗? Tks

你好 ,pdjuandi:

Tks、以供 您解释。 我想我们现在在这个编解码器中更加清楚了。

还有另一个与开关输入源相关的问题。

客户将 MIC 输入设置为 PIN 12.13

将 FM 输入设置为引脚14 16。

因此、工作逻辑是 在 FM 和 MIC 之间选择两者中的一个。

寄存器如下所示:

MIC 打开、FM 关闭:

R17=0xFF

R18=0xFF

R21=0x00

R22=0x00

MIC 关闭、FM 打开:

R17=0x0F

R18=0XF0

R21=0111 1000

R22=0111 1100

基于此逻辑、我们发现使用 FM 时、我们仍然可以听到 MIC 发出的声音、 我认为可能缺少一些寄存器来阻止 MIC 进入 FM 信号。

为你的导游准备的 Tks!

以下是建议的设置、开开关的定义意味着路径未激活、闭合意味着路径处于激活状态。

上述设置与之相反。

这是我看到他们想要配置编解码器的内容、但请与他们确认并在需要时进行更改。

此致。

你好 ,pdjuandi:

Tks 供您回复。 正如我看到的,MIC Close,FM open case 存在混乱。

[引用 userid="35889" URL"~/support/audio-group/audio/f/audio-forum/1126477/tlv320aic3104-right_lop-lom-output-issue/4221322 #4221322]MIC (MIC1RP/M 至右侧 ADC) Close、FM (MIC2L 至左侧 ADC、MIC2R 至右侧 ADC) Open case:关于此设置,我可以看到 FM 信号(MIC2L/R)都没有连接到 L/R ADC PGA,为什么我们将 FM 打开?