您好!

我正在使用 TLV320ADC 和 ESP32录制音频。 录制的音频在噪声方面很好、但看起来信号是以低8倍的速率离散化- I2S 数据中的每个采样重复8次。

我的目标是22050Hz 的双通道16位音频;我已设置 I2S 连接、并连接 BCLK、WCLK 和数据(无 MCLK);

I2S 配置:

静态常量 I2S_CONFIG_t I2S_CONFIG ={ .MODE =(I2S_MODE_t)(I2S_MODE_MASTER | I2S_MODE_RX)、 .SAMPLE_RATE = SAMPLE_RATE、 .BISTS_PER_SAMPLE = I2S_BLE_SAMPLE_16BIT、 .CHANNEL = I2S_FMT_LEFT 、I2S_COMM_COMM_COMMON_COMM_COMMAND_COMMAND_B = LEVACATION = I2S_LEFT_COMMAND_COMMAND_COMMAND_B intr_alloc_flags = 0、//默认中断优先级 .dma_buf_count = 32、 .dma_buf_len = 1024、 .use_apll = true、 .TX_desc_auto_clear = false、 .fixed_MCLK = 0 };

和 TLV 注册表设置:

tlv320_selectPage (0); i2c_write_reg_BYTE (1、0x01);//重置 vTaskDelay (20 / portTIk_Period_MS);//提供20ms i2c_write_reg_BYTE (4、0x05);// Clocl-gen 多路复用-使用通过 ESP I2S 发出的 BCLK 时钟 I2C_WRITE_REG_BYTE (5、0x11);//禁用 PLL i2c_write_reg_BYTE (18、0x81);// NADC = 1、分频器加电 i2c_write_reg_BYTE (19、0x82);// mAdc = 2、分频器加电 i2c_write_reg_BYTE (27、0x00 ); / select_trl 1 (0x22);/ select_length (0x32);/ trl 1、ip_re_trl 1、ip_trl (0x32);/ self 1、ip_length (1) //左 PGA 的左侧 ADC 输入选择= IN1L (P)作为单端 i2c_write_reg_BYTE (55、0xFC);//右 PGA 的右侧 ADC 输入选择= IN1R (M)作为单端 i2c_write_reg_BYTE (59、0x00);//左侧模拟 PGA 选择= 0dB idb_write_byte (0x2c );// vc2c_reg_byte (0x2c);// tc2 (0x2c);tc2 (0xc2) //为左侧 ADC 和右侧 ADC 加电 i2c_write_reg_Byte (82、0x00);//取消静音

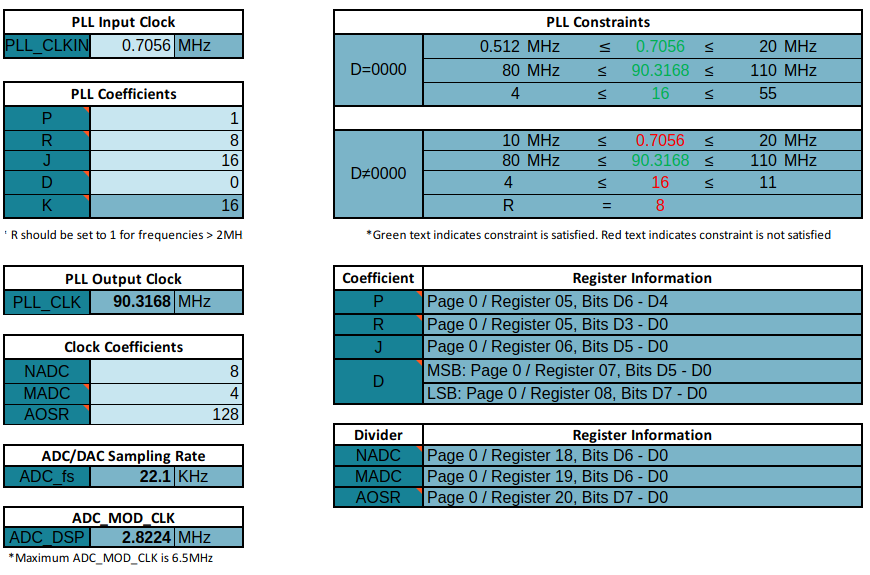

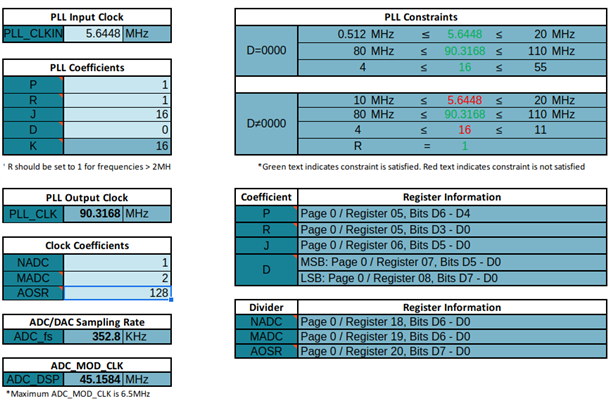

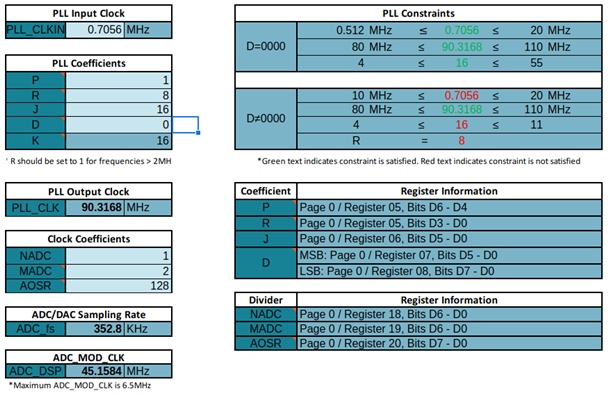

我尝试使用以下命令启用 tlv 的 PLL:P:1 R:8K:16 NADC:8mAdc:4 AOSR:128、但它没有产生任何有用的结果。

欢迎您提供任何帮助、让 TLV 以更好的质量进行记录。