Other Parts Discussed in Thread: PCM1840

您好!

我们的客户计划在从模式下使用 PCM1840。

要查看他们从 DSP 输入的 BCK 时钟时序、我们应该参考哪一个规格?

第6.6节时序要求注意到“所有输出”,我们期望此规范处于主模式 PCM1840将输出如下时序规范所示的 PCM 数据。 是这样吗?

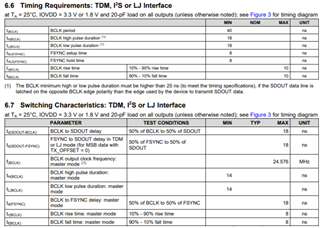

6.6时序要求:TDM、I2S 或 LJ 接口

在 TA = 25°C 时、IOVDD = 3.3V 或1.8V、所有输出上的负载为20pF (除非另有说明);时序图请参见图3

另一个好奇心是数据表中上升和下降时间的定义、对于输出节点10-90%是合理的。

但是、对于作为受控模式 BCK 引脚输入的输入节点、时钟时序可能由 Vth H (max)和 Vth L (min)定义、它不是10%-90%。 我们能否在从模式下读取具有此定义的规范?

TR (BCLK) BCLK 上升时间 10%- 90%上升时间 10ns

TF (BCLK) BCLK 下降时间 90%- 10%下降时间 10ns

因为、大规模生产产品具有用于这些时钟线路的转储电阻器。 为了获得更好的 EMI 特性、上升和下降时间变得更长。

此致、

Mochizuki