Other Parts Discussed in Thread: PCM1864-Q1, PCM1864

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/998136/pcm1864-q1-gain-problems

器件型号:PCM1864-Q1主题中讨论的其他器件:PCM1864

大家好!

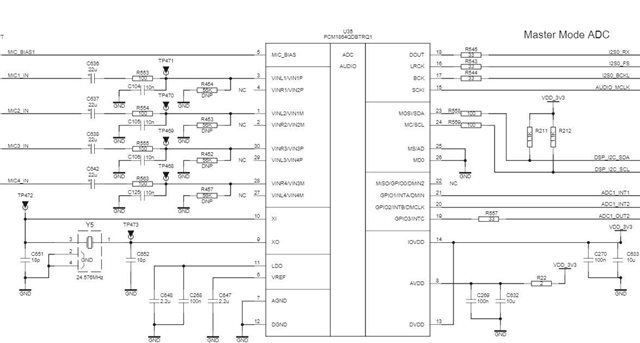

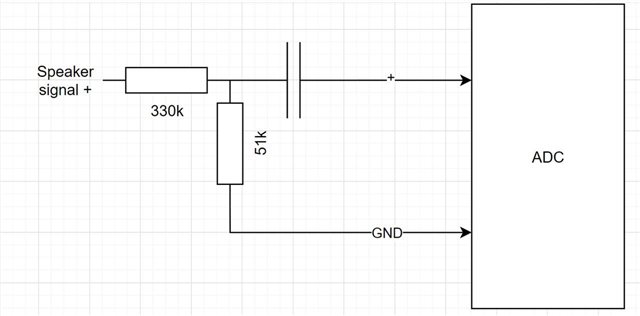

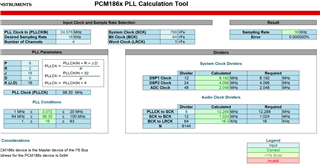

我们的输入信号有问题、我们有以下连接方案:麦克风连接到 CH1 L、带分频器的扬声器信号连接到 CH2 L。问题如下: 麦克风信号的放大率针对任何通道(CH1 L / CH2 L)进行了正确调节、并且扬声器在任何数字或模拟增益值下的信号电平都保持在极低的水平、几乎听不到。 我曾或两次观察到一张图片、显示在最大数字增益下信号非常强、但现在这仍然不起作用。 请告诉我您对此有什么想法吗?

BES 此致、

Georgy Zagoruiko