Other Parts Discussed in Thread: SRC4382

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1001945/src4382-src4382-pin-35-and-36

器件型号:SRC4382大家好、

如果将引脚31和32用作 SRC4382作为 AES 输出、如何使用引脚35和36或如何配置引脚35和36?

BR

很好

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: SRC4382

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1001945/src4382-src4382-pin-35-and-36

器件型号:SRC4382大家好、

如果将引脚31和32用作 SRC4382作为 AES 输出、如何使用引脚35和36或如何配置引脚35和36?

BR

很好

您好、您好、

不必使用引脚35和36、但引脚是可选 的、并提供额外的功能。 它们可用于 DIR 或 DIT、如下所示:

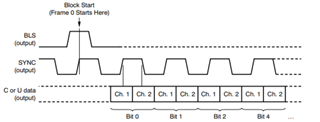

AES3编码器包括一个块启动输入/输出引脚、BLS (引脚35)。 BLS 引脚可编程为输入或输出。 BLS 引脚的输入/输出状态通过控制寄存器0x07中的 BLSM 位进行编程。 默认情况下、BLS 引脚配置为输入。 作为一个输入、BLS 引脚可被用来强制一个块启动条件、通过为下一个数据帧生成一个 Z 前导码来启动一个通道状态和用户数据的新块。 BLS 输入必须与 DIT 内部同步时钟同步。 该时钟在 SYNC (引脚36)上输出。 同步时钟上升沿与 DIT 输出的 AES3编码数据的每个帧的开始对齐。 图66说明了外部块启动信号所需的格式、并在 BLS 引脚配置为输出时指示了该格式。 当 BLS 引脚为输出时、DIT 会根据内部同步时钟生成块启动信号。

通道状态和用户数据位也可以通过通用输出引脚 GPO[4:1]进行串行输出。 图71显示了用于此目的的 GPO 引脚的输出格式、以及 DIR 块启动(BLS)和帧同步(SYNC)时钟。 DIR 同步时钟输出的上升沿与接收到的 AES3数据的每个帧的开始对齐。

最棒的

Zak