Other Parts Discussed in Thread: TLV320AIC24K, TLV320DAC32

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TLV320AIC24K 主题中讨论的其他器件: TLV320DAC32

尊敬的 TI:

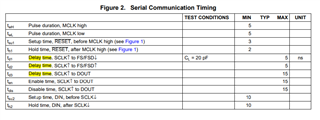

关于为 TLV320AIC24K 串行通信提供的时序限制、我需要一个帮助。 在这里 、↓延时的最短时间、没有给出 SCLK↑到 FS/FSD 的时间。 ↑延迟时间、SCLK↑至 FS/FSD 未给出。 与此类似, 数据表中没有给出最大设置时间 DIN,SCLK↓之前,以及最大保持时间 DIN,SCLK↓之后。 我们需要为他们考虑什么价值、您能澄清这些缺失的信息吗? 我们需要这些信息来增加 FPGA 的时序限制。 我附上了一个时序信息图像以供参考。

此致、

Deepeshwar