您好!

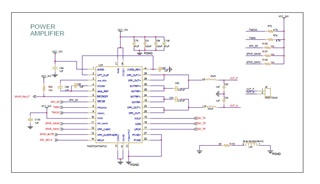

我们使用的是 TI 的汽车 D 类音频放大器'TAS5720ATDAPQ1'、而我们使用的控制器是 Atmel 的'ATSAMV70Q20B-AAB'。

即使我们能够生成具有以下频率和适当时钟比率的所有 I2S CLKS、音频输出也不会生成。

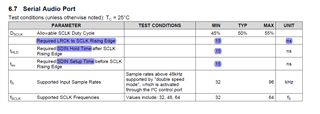

采样率:48KHz

用于生成 TK 和 TF 的内部 SSC MCLK:150000000

MCLK:12.28MHz

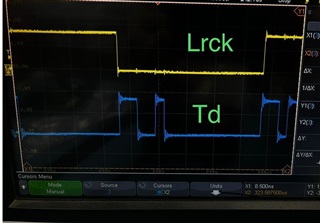

位 CLK (TK):1.53MHz

字 CLK (TF):48.00 KHz

数据(TD):数据- 16位

位 CLK 与字 CLK 的比率:32 (即使我们尝试了64)

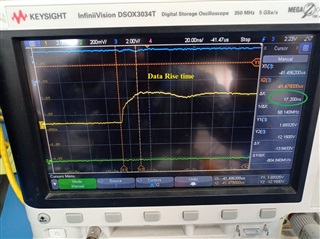

我们观察到故障寄存器(0x08、值:0x08)中的位'CLKE'正在被置位、指示'非锁存间歇性时钟错误'。

我们还观察到故障引脚持续脉冲(每350us 间隙为10us、较低)。

加电并读取故障寄存器后、我们连接了切换 SPK_SD 引脚并将其连接到 SPK_FAULT 引脚、但即使这样也没有帮助。

请告诉我们该误差(CLKE 位被设定)是由于不正确的时钟比率或者时钟中的任何失真/延迟而产生的。

放大器原理图部分的快照随附、供您参考。 还附加了一些 I2S 时钟/数据波形。

此致、

Imran、

MJM Technologies、班加罗尔