Other Parts Discussed in Thread: PCM1808

您好、Sirs、

PCM1808数据表指定了 TLRDO 的最大值40ns、而客户从 LRCK 边缘到 DOUT 的最大值为372ns。 您是否会建议此测量对 PCM1808是否有效?

谢谢、此致、

陈耀恩

2020年8月1日

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Wayne、

此规格已通过设计仿真和基准测量进行验证、372ns 看起来相当不错。 采样率为48kHz 的 BCLK 周期为325ns、因此它们似乎将数据位与错误的时钟边沿相关联? 他们可能还希望仔细检查示波器设置、并确保输入未设置为限制带宽。 为了重现数据表结果、它们还应遵循脚注1中提到的测试条件:"输入的时序测量基准电平为1.4V、输出的时序测量基准电平为0.5VDD。 上升和下降时间为输入输出信号摆幅的10%至90%。 DOUT 的负载电容为20pF。 t (SCKI)是 SCKI 周期。"

最棒的

Zak

你好、Zak、

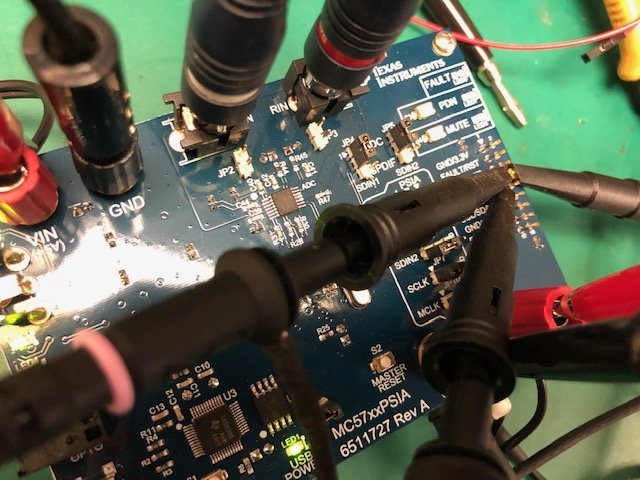

我可以再现客户对 MPAA MC5CXXPSIA 板上 PCM1808器件的问题。

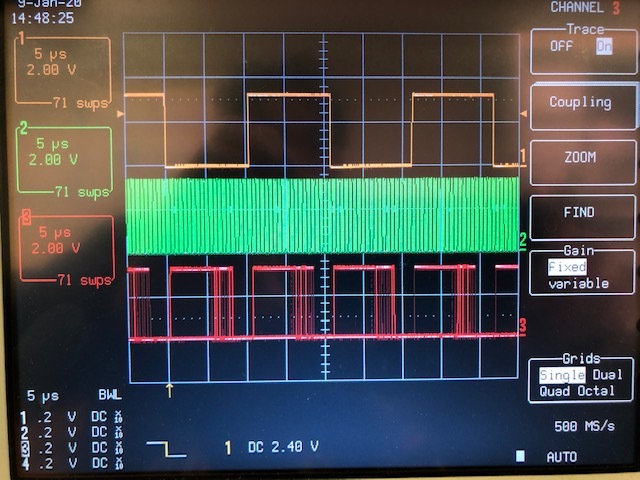

借助3.3V 逻辑和48kHz 采样率、我可以观察到 LRCK 沿和 DOUT 沿之间的352ns 延迟时间。

CH1 = LRCK、CH2 = BCLK、CH3 = DOUT (VIL (max)= 0.8V、VIH (min)= 2.0V)

放大(LRCK 下降沿至 DOUT 上升沿)

LRCK 上升沿到 DOUT 上升沿

根据 I2S 规范、DOUT 应以 BCLK 为基准、而不是以 LRCK 为基准。 I2S 规范未指定 LRCK 边沿到 DOUT 边沿、而是 BCLK 边沿到 DOUT 边沿之间的规格、DOUT 的 MSB 从第二个 BCLK 时隙开始。

我认为 LRCK 边沿到 DOUT 边沿的规格是针对 LJ 格式而不是 I2S。 我们应该增加另外325ns (一个 BCLK 周期)以符合 I2S 规范。 325ns + 40ns + 40ns = 405ns 的实际延迟对于 I2S 应有效。 对于 PCM1808器件和 I2S 规格、客户的372ns 测量值应该是可以接受的。

如果我的陈述缺失或错误、请随时通知我。

谢谢、此致、

陈耀恩

2020年9月1日