Other Parts Discussed in Thread: TAS2559, TAS2557, TMS320F28015, TAS2559EVM, TAS2505, TAS2563, TAS2552, TAS2555

主题中讨论的其他器件: TAS2557、 TMS320F28015、 TAS2505、 TAS2563、 TAS2552、 TAS2555

您好!

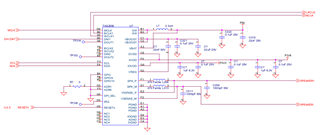

我正在评估 TAS2559、希望在现有设计中使用它(或 TAS2557)替代 Cirrus Logic/Wolfson WM9081。 WM9081使用以下配置:

- 输入时钟为15MHz。 该时钟来自 TMS320F28015、并连接到 WM9081的 MCLK 输入。

- WM9081将15MHz 时钟一分为二、从而生成7.5MHz 的内部 FLL 参考时钟。

- WM9081的 FLL 用于生成11.29MHz 的内部 CLK_SYS。

- WM9081可生成705.62kHz 的 BCLK 和22050Hz 的 LRCLK。 BCLK 和 LRCLK 是从 WM9081到 FPGA 的输出。

- FPGA 使用 BCLK 和 LRCLK 来生成一个连接到 WM9081的 DACDAT 输出。

- WM9081使用 D 类放大器将来自 FPGA 的 DACDAT I2S 数据流转换为单声道音频。

- TMS320F28015的 I2C 接口用于配置 WM9081并在运行期间控制音量。

TAS2557或 TAS2559看起来可能替代 WM9081、但由于我们使用了非标准时钟和 TAS 系列器件的有限文档、因此配置似乎是一个问题。 因此有以下问题:

- TAS2557或 TAS2559是合适的选择吗? 请注意、我们迫切需要。 没有库存的更好器件不是解决方案。

- 如果只需要一个 I2S 接口、TAS2557和 TAS2559引脚是否兼容?

- 在给定15MHz 输入的情况下、是否可以将 PLL 配置为生成适用于22050采样率的时钟?

- 是否有任何有关 PLL 的官方文档? 我看到另一个用户设法对部分 PLL 进行反向工程(tas2559 PLL 和时钟配置)。 (我不得不说、他不得不这么做是非常令人失望的。)

- 假设 PLL 可用于从15MHz 生成11.29MHz、需要观察到哪些 PLL 限制(VCO Fmax、Fmin 等)?

请注意、虽然这些器件的许多 DSP 特性看起来非常有趣、但我们迫切需要 I2S 将音频单声道输出到4欧姆扬声器。 在可预见的未来、我们将使用 ROM 模式1。

目前、我在这里有一个 TAS2559EVM、我希望能够将一些导线连接到我们现有的 WM9081板上、以便试用 TAS2559、但 PPC3在时钟配置方面似乎非常有限。 此时、我似乎最好的做法是通过 I2C 来获取寄存器、但我不想在不知道 TAS2557或 TAS2559将执行我想要的操作的情况下沿着该路径前进。

感谢你的帮助。

加伦