Other Parts Discussed in Thread: PCM3060

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/964833/pcm3060-about-bck1-2-high-low-time

部件号:PCM3060您好!

关于 PCM3060上的 BCCK1/2高/低电平时间、我的客户正在提出一个问题。

(问题)

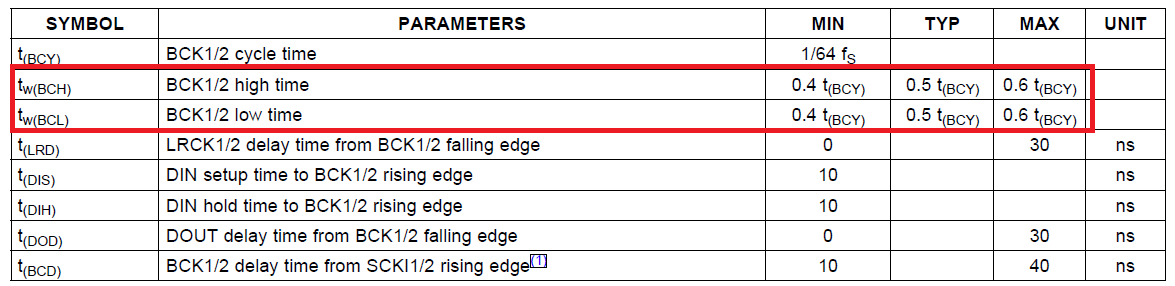

根据数据表图24、BCK1/2高电平/低电平时间描述如下。

为什么这些时间的范围是40%到60%? 为什么这些不固定为50%?

他们认为 bck 除以 SCKI。 此时、bck 和 SCKI 是整数的偶数比。

因此、占空比应固定为50%。

请告诉我们、为什么这些时间的范围是40%到60%?

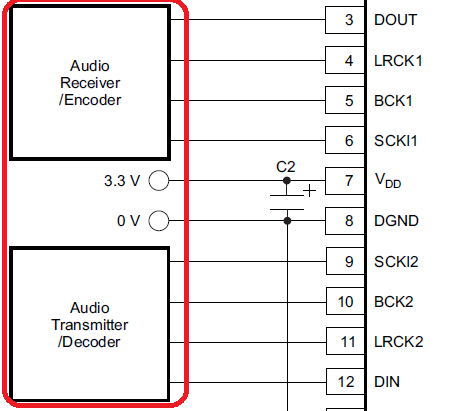

(我的客户配置)

・LRCK=1fs

・bck=64fs

・SCKI=512fs

(bck = 1/8 * SCKI)

*在上述情况下,占空比是否固定为50%?

此致、

TAO_2199