主题中讨论的其他器件:PCM1864、 TIDA-01454

尊敬的团队:

我的客户正在从模式和 TDM 模式下使用 PCM1864、具有2个 MMC+2扬声器单端输入。

他们的开发过程实际上受到了两个因素的阻碍。 请帮您解决这些问题? 谢谢!

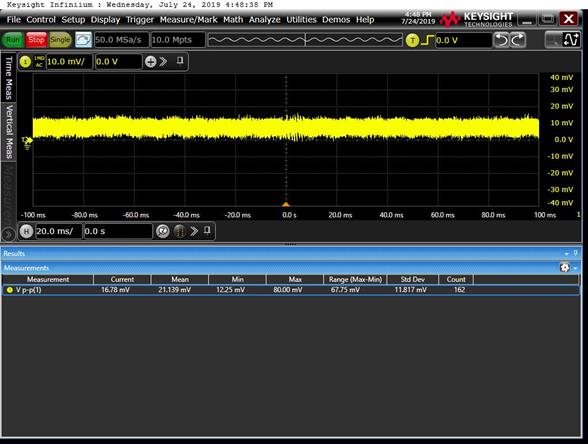

当 VIN3P 和 VIN4P 引脚没有信号输入时、客户仍会在从 DOUT 提取 VIN3P 和 VIN4P 数据时收到一些噪声。

您认为在没有输入信号通道的情况下会导致这些噪声的原因是什么?

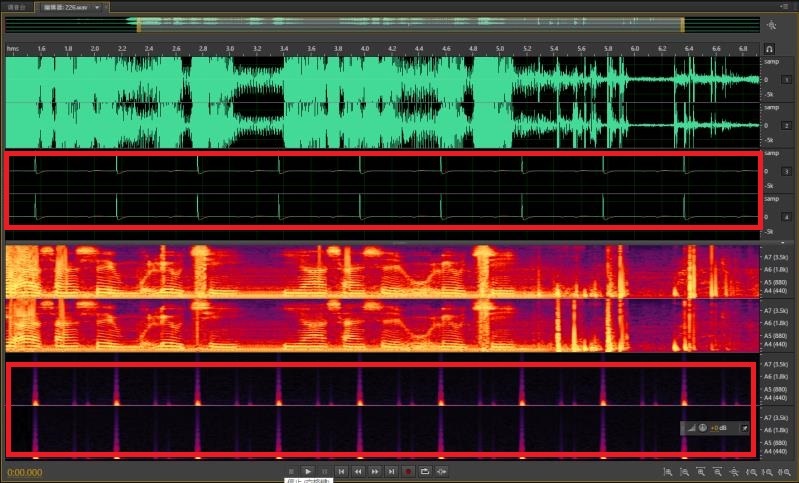

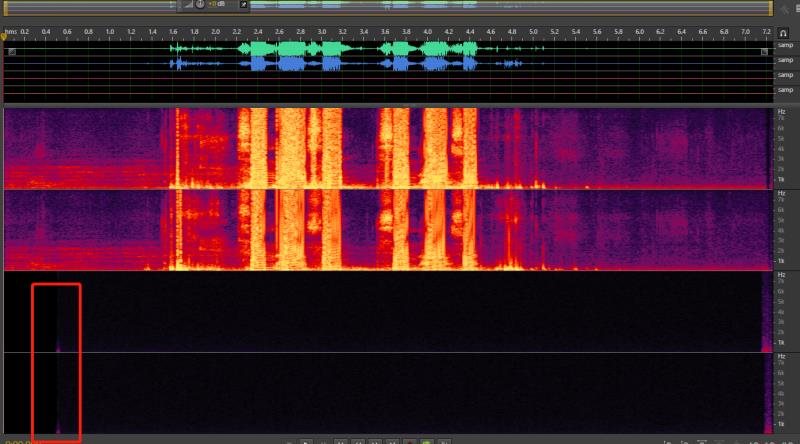

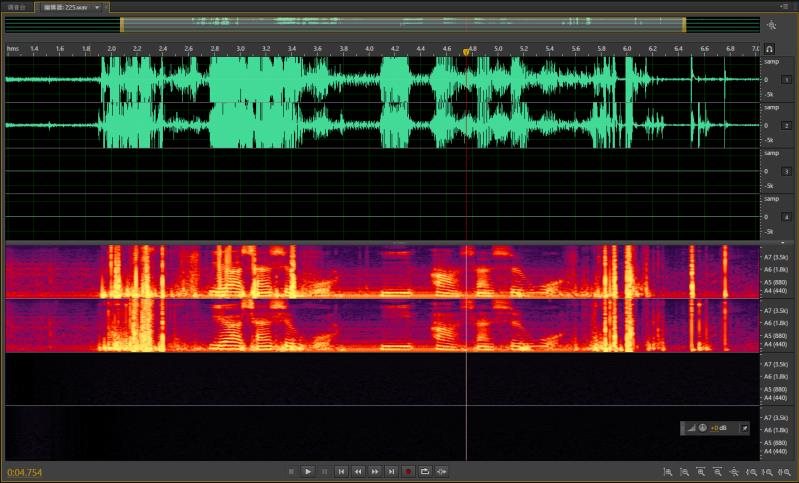

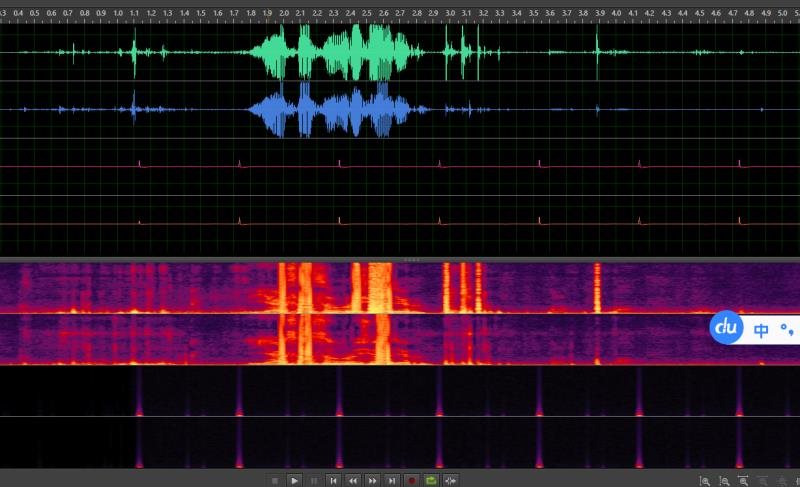

我们在 4个条件下测试了噪声:只有当 ADC 静音时、噪声才会消失。 从 DOUT 提取 VIN3P 和 VIN4P 数据时的噪声测试结果如下图所示(在图中、绿色结果为 dB、红色结果为频率瀑布)。

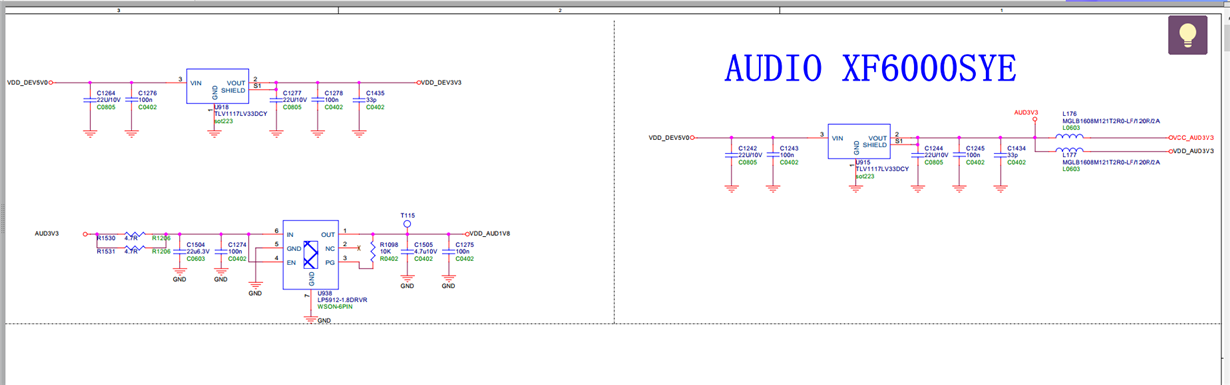

1.1将 VIN3P 和 VIN4P 的 ADC 取消静音、如原理图所示配置 VIN3P 和 VIN4P;结果: 大噪声。

1.2对 VIN3P 和 VIN4P 的 ADC 取消静音、将 VIN3P 和 VIN4P 引脚连接到 GND;结果: 噪声极小。

1.3将 VIN3P 和 VIN4P 的 ADC 取消静音、不将任何器件连接到 VIN3P 和 VIN4P 引脚;结果: 噪声极小。

1.4将 VIN3P 和 VIN4P 的 ADC 静音、按原理图所示配置 VIN3P 和 VIN4P;结果:无噪声。

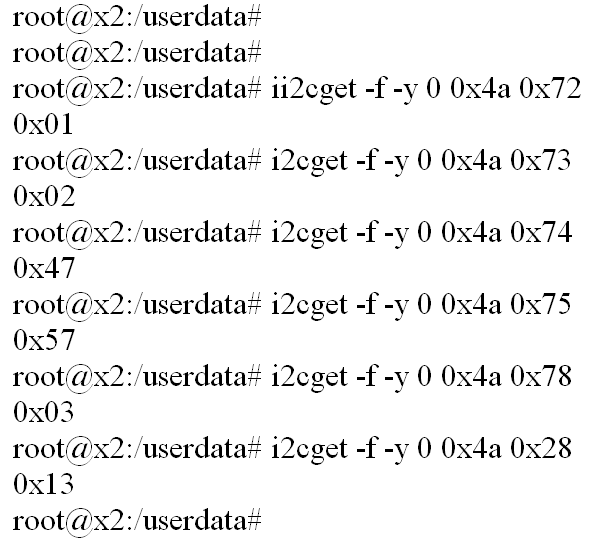

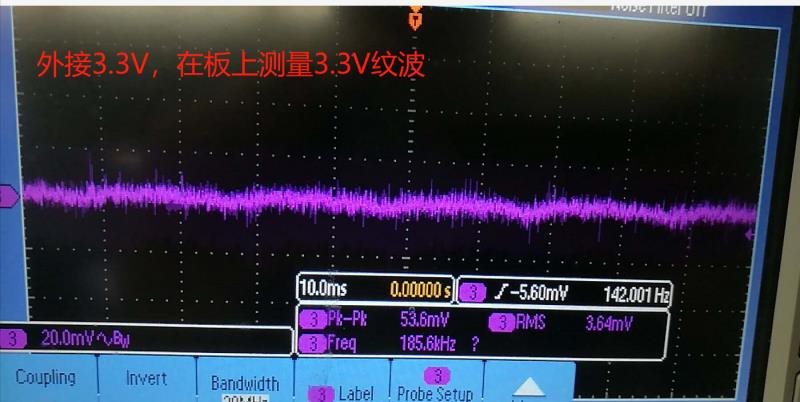

2、如下结果所示、寄存器0x72~0x78可以显示器件 DVDD 和 LRCLK 错误、但器件可以获得 DOUT。 这是奇数状态吗?

这是从 DOUT 提取 VIN3P 和 VIN4P 数据时产生噪声的原因吗?

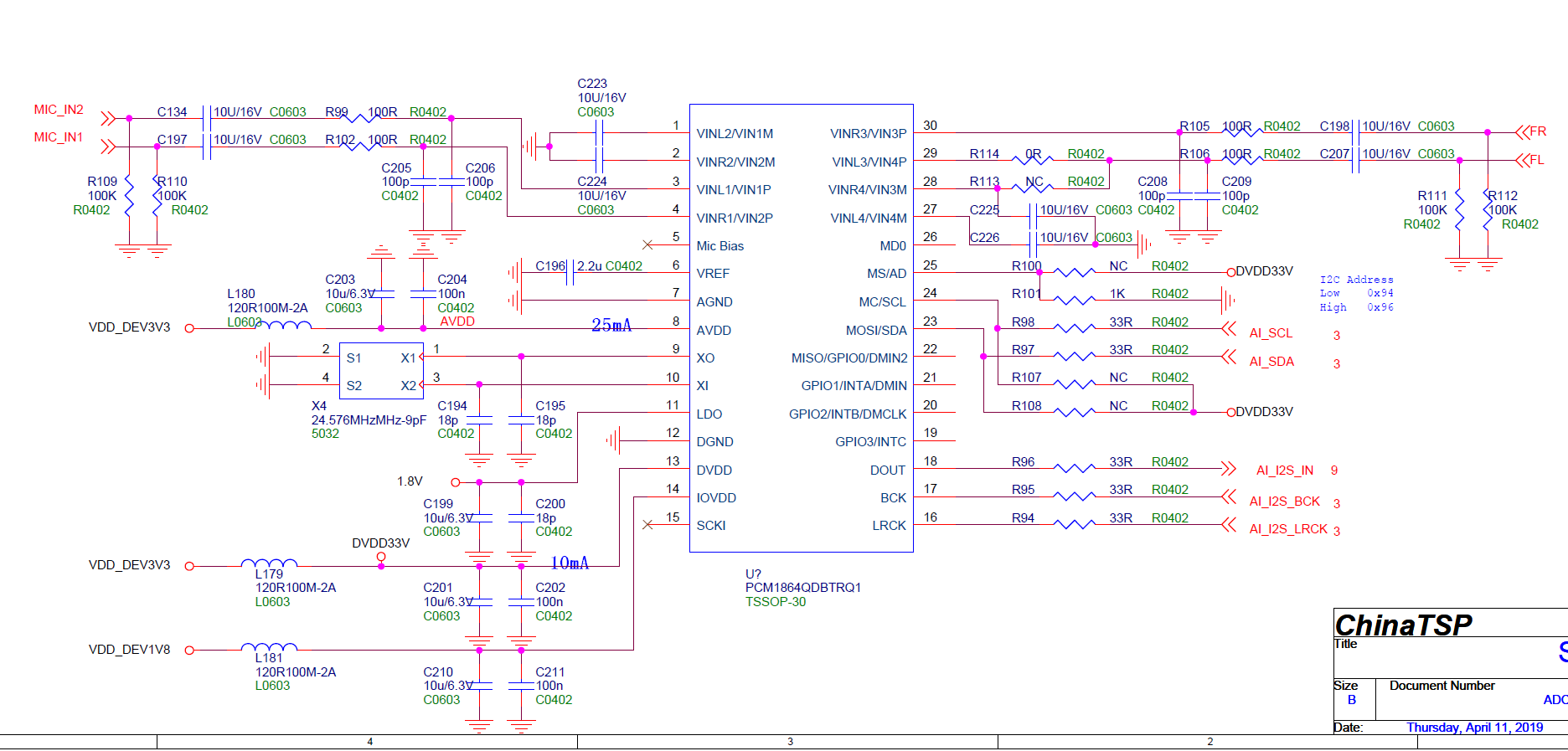

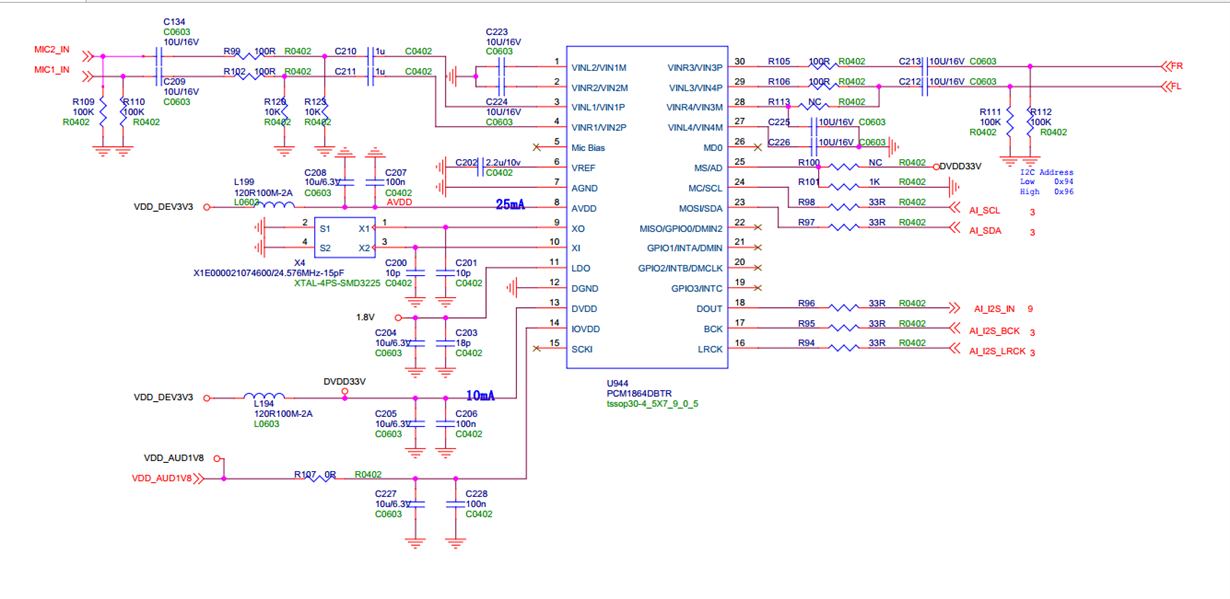

以下是它们的原理图和寄存器配置(根据 TIDA-01454)、供您参考。

受控和 TDM 模式寄存器

寄存器 值

0x00 0x00 //更改为第0页

0x01 0x20 // PGA CH1_L 至16dB

0x02 0x20 // PGA CH1_R 至16dB

0x03 0x20 // PGA CH2_L 至 16dB

0x04 0x20 // PGA CH2_R 至 16dB

0x05 0x87 //启用平滑 PGA 更改;独立链接 PGA;启用自动削波抑制

0x06 0x41 //极性:正常、通道:VINL1[SE]

0x07 0x41 //极性:正常、通道:VINR1[SE]

0x08 0x44 //极性:正常、通道:VINL3[SE]

0x09 0x44 //极性:正常、通道:VINR3[SE]

0x0A 0x00 //次要 ADC 输入:无选择

0x0B 0xdf // RX WLEN:16位;TX WLEN:16位;FMT:TDM 格式

0x0C 0x01 // 4通道 TDM

0x10 0x00 // GPIO0_FUNC–GPIO0;GPIO0_POL -正常

0x11 0x50 // GPIO3_FUNC - DOUT2;GPIO3_POL -正常

0x12 0x00 // GPIO0_DIR - GPIO0 -输入

0x13 0x40 // GPIO3_DIR–GPIO3–输出

0x20 0x61 // MST_MODE:从器件;不使用晶体、因此将 SCK_XI_SEL 设置为 SCK;CLKDET_EN:启用