主题中讨论的其他器件:TAS2505

尊敬的 TI:

由于 MCU 限制、我们没有通用音频采样率、例如8k、16k、48kHz。 目前、我们有10k、25k 和50kHz 选项。 以下是应用电路:

- TAS2505-Q1是不具有 MCLK 输入的 I2S 从器件

- 使用 BCLK 作为 PLL 时钟输入

- SPKVDD 仅为5V、IOVDD 仅为3V3

- LDO_SEL 为高电平、使用内部 LDO 将 AVDD 和 DVDD 连接在一起

- I2S:BCLK=800kHz、WS=25kHz、16位深度

我已经测试了另一个具有相同配置但采样频率为48kHz 的介质源,它工作正常。 然后、我修改了时钟设置以满足 TAS2501-Q1要求。 我的设置如下:

- BCLK 为800kHz、作为 PLL_CLKIN

- P=1、R=4、J=28、P=1

- PLL_CLK 为89.6MHz、作为 CODEC 的 CLKIN

- NDAC=2、DAC_CLK 为44.8MHz

- MDAC=7、DAC_MOD_CLK 为6.4MHz

- DOSR=256、DAC_FS 为25kHz

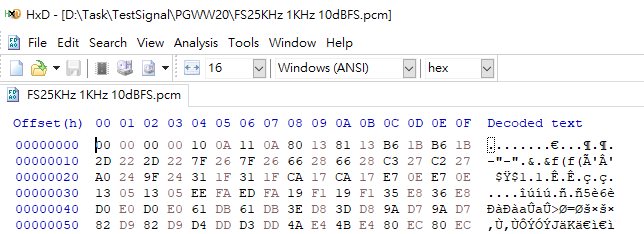

有关更多详细信息、请参阅随附的配置 file.e2e.ti.com/.../PGWW20_5F00_ClassD_5F00_playback_5F00_FS25k.cfg

但是、我听到的是高频音调、而不是1kHz 音调。 我要确认的是什么