您好!

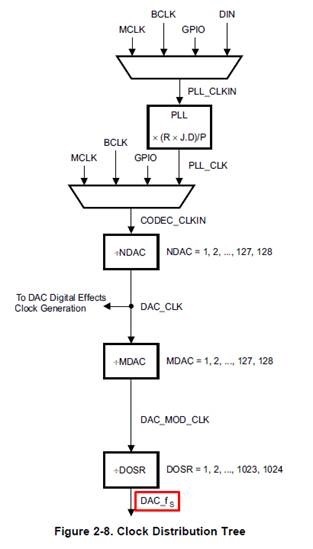

我对 TAS2505中的 ADC_FS 有疑问。 "参考指南"中的时钟分配树如下所示:

有许多设置会影响 DAC_FS: PLL 中的 R、J、D、P 以及 NDAC、MDAC、DOSR。

我的问题是、DAC_FS 是否必须等于 I2S 输入上采样率(WCLK)的整数乘法(或除法)?

我使用 TAS2505EVM 评估板、并注意到无法更改该评估板上的 I2S WCLK。 无论从 PC 播放的音频文件的采样率如何、它都固定在48kHz 上。 该电路板上的流控制器(TAS1020)可能会负责提供此类频率、并且无法更改此频率。

在 TAS2505EVM GUI 中使用数字设置时、我可以设置不同的 DAC_FS 值(具有恒定的 WCLK 48kHz)、DAC_FS 中的这些变化对声音质量有很大影响。 在使用 TAS2505的器件中、我可以设置不同的采样频率(WCLK)。 我不使用 MCLK 作为 DAC 时钟源、而是使用具有 PLL 的 BCLK。 因此、我想我需要选择正确的 I2S 采样率和 DAC_FS 以获得最佳音质、但我不知道我在上面提出的问题的答案。

谢谢、此致/ Maciej