主题中讨论的其他器件: PCM5122

您好!

我做了另一个硬件开发、允许对 PCM5242进行软件模式配置、我希望将该芯片配置为与基于48kHz 音频的输入 I2S 流配合使用。 数据表中引用了 SLAC622、该产品似乎不再存在(如果我搜索论坛的内容正确、也可能从未存在)。

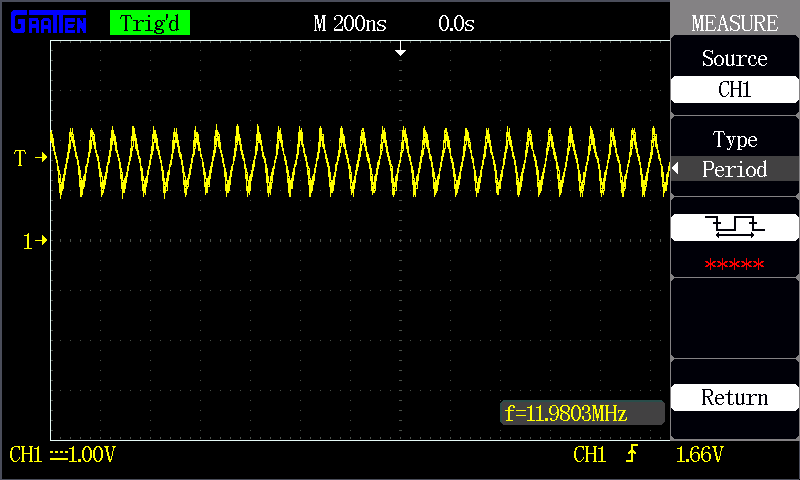

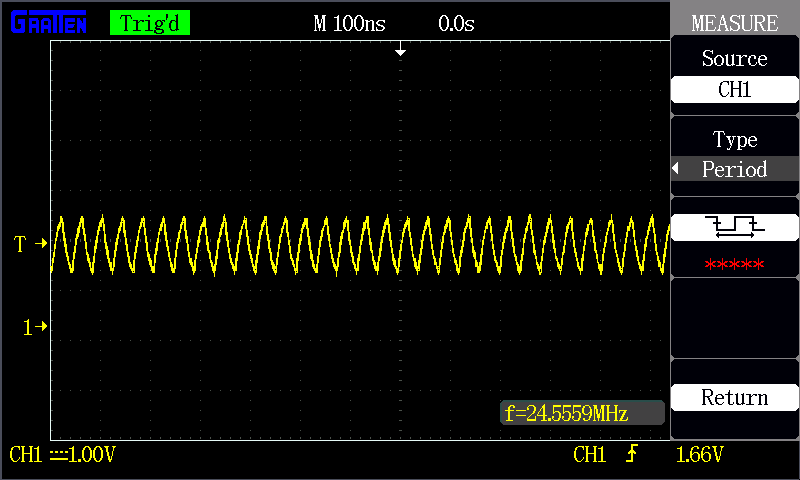

我一直遵循数据表的第8.8.7节("非音频速率主时钟的时钟主器件")、并已将 GPIO6配置为具有12MHz 时钟的 PLL 输入。 PLL 配置为以98.304MHz (R = 1、J = 8、D = 1920、P = 1)运行。 我已将 GPIO5配置为 PLL/4的输出、即24.576MHz。 我已将 DAC 配置为使用 SCK 作为参考时钟。

现在、我正在尝试了解如何处理 bck 和 LRCK;大概这些需要与 SCK 对齐(跳线连接到 GPIO5、因此以24.576MHz 运行)。 数据表的第8.8.7节似乎提到了这些是 PCM5242的输出。 但是、我不理解这是如何工作的、因为我的 USB 转 I2S 级(CP2615)输出4个 I2S 信号、所以我不确定如何纠正这种情况。

CP2615 | PCM5242

->SCLK (位时钟) ->| o-bck (引脚27)

->MCLK (12MHz) ->| O- GPIO6 -> PLL -> GPIO5 -> SCK (引脚26)

->数据(DATA) ->| O- DIN (引脚28)

-> LRCK (左/右)->| O- LRCK (引脚31)

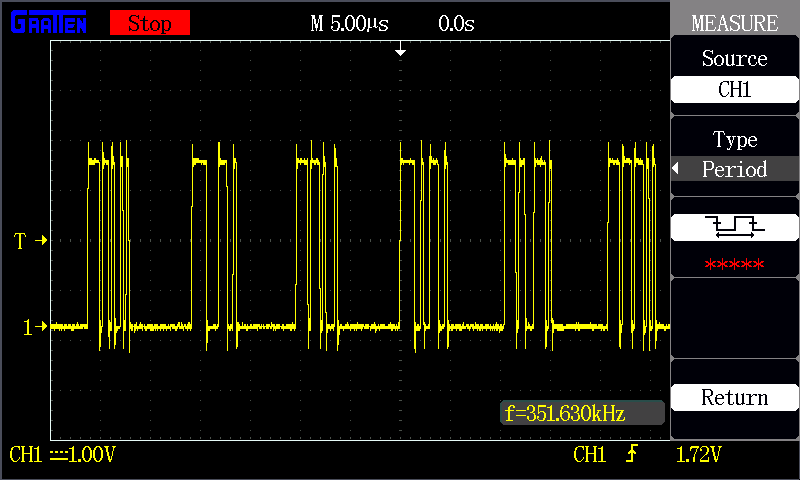

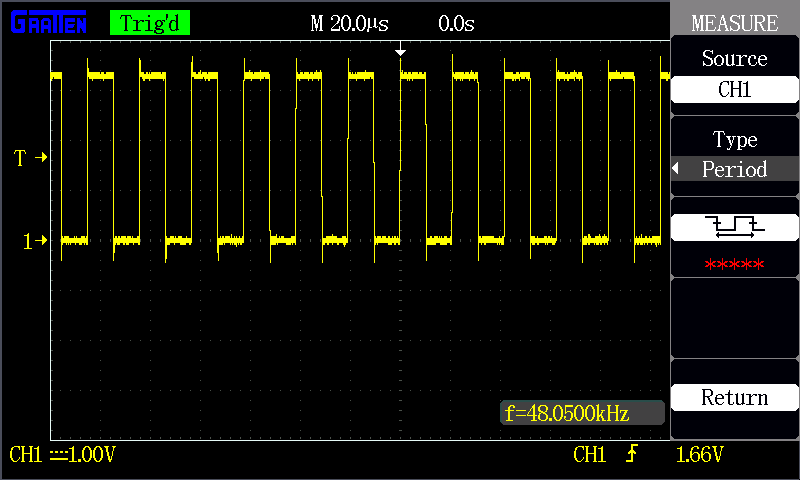

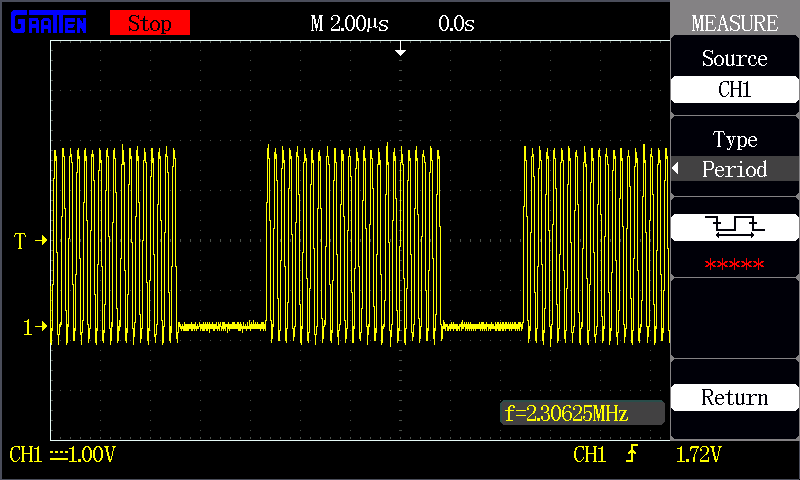

感谢您提供的任何帮助! 我已经对信号进行了范围划分、它们看起来是我所期望的(GPIO5输出24.576MHz)。 为了踢脚、我连接了 BCK、DIN 和 LRCK 信号、但寄存器91读取0x30、这表明 SCK 不是采样时钟的有效比率。

谢谢你