https://e2e.ti.com/support/audio-group/audio/f/audio-forum/799875/tlv320aic10-audio-forum

器件型号:TLV320AIC10主题中讨论的其他器件: TLV320AIC3100

您好!

我们的客户面临的问题是 TLV320AIC10器件有点旧。

在主控模式下、AIC10生成 SCLK 和 FS 时钟。 但是、这些输出时钟 本身将违反 DAC 数据输入设置时间要求。

这是模式设置和输入 MCLK 频率。

M1=1 M0=1 M/S=1帧同步(FS)功能—主模式

Register1=0x04 (抽取/FIR 旁路)

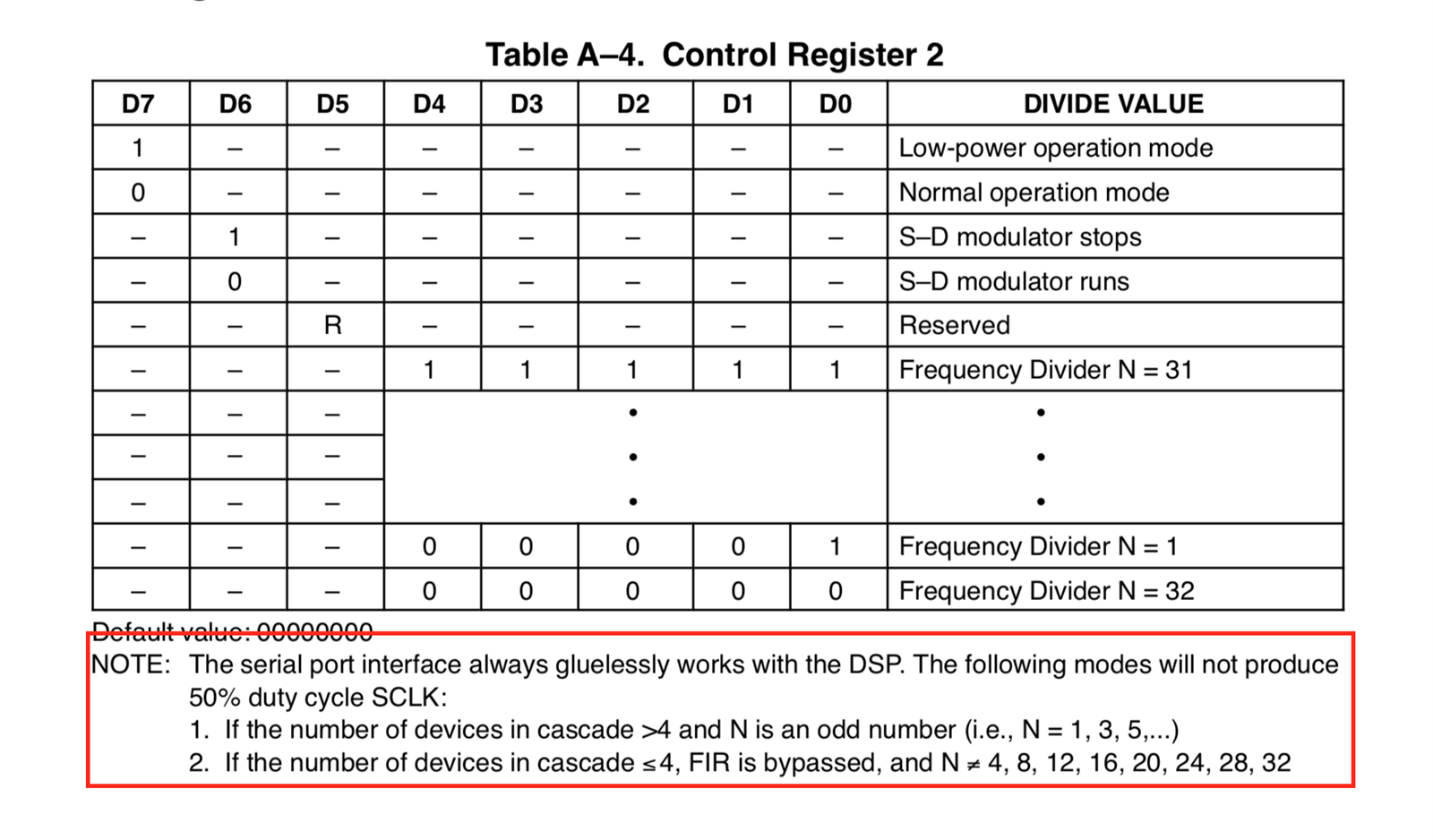

寄存器2=0x06 (N=6)

Register3=0x01 (16位数据格式)

寄存器4=0x00 (DAC PGA 增益=0dB)

MCLK = 19.6608MHz

捕获的波形如下所示。

由于这种 FS-SCLK 时序违例、我们的 DSP 无法捕获合适的第一个 SCLK 下降沿、从而将16位 MSB 数据输出到 DAC、并违反 tsu 要求。

Q1:SCLK 时钟似乎是4位块化输出、它是不寻常的 SCLK 格式、通常音频转换器 SCLK 输出是连续时钟。 AIC10内部时钟分频器的功能是否正确?

Q2:当我们使用生成的来自主模式 AIC10的这种非常窄的 FS 下降沿到 SCLK 下降沿的时钟时序时、是否有任何好的解决方案来保持 DAC 数据输入的设置时间 Tsu 5nsec (mini)要求?

此致、

Mochizuki