大家好、我将使用 TLV320ADC6120开发一个采集板

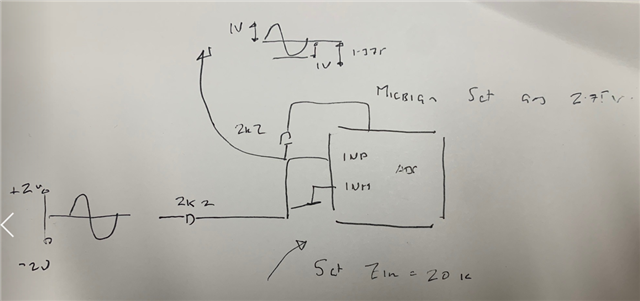

我有 一个振幅为+/- 2Vpp 的输入信号在0V 时发出。

我使用了 MICBIAS/2 输出将信号转换到0-2.75V 范围、使用该输出创建共模电压是否正确?

我需要具有直流耦合信号。

我将 ADC 配置为 Σ-Δ 输入 模式直流耦合。 (IN1P、IN1M=GND)、对吗?

我采集的数字信号在上侧似乎已饱和、如果我将通道配置为差分模式、我会看到相应的输出。

配置 寄存器 BIAS_CFG 寄存器(地址= 0x3B)我也遇到问题、表8-84中引用的 VCM 的含义是什么? 能否使用具有 VCM 电平 的 MICBIAS 来移动信号?