主题中讨论的其他器件: TAS6424E

大家好、团队、

我的客户在启动时对 TAS6422E-Q1有一个问题。

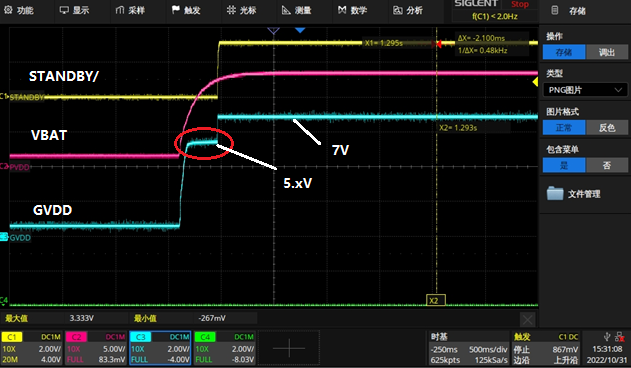

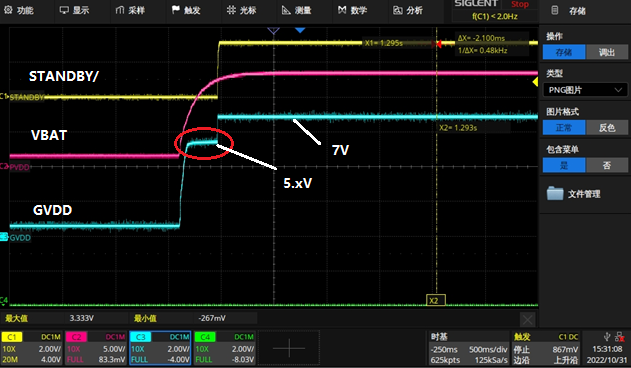

下面是启动波形、我们发现在启动时会有一个 GVDD 阶跃、大约为5.XV、然后将上升至正常7V。

问:此 GVDD 5.XV 步骤是否是预期中的正常行为? 如果不是、您能否提供一些建议来确定根本原因?

谢谢。

Johnny

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、团队、

我的客户在启动时对 TAS6422E-Q1有一个问题。

下面是启动波形、我们发现在启动时会有一个 GVDD 阶跃、大约为5.XV、然后将上升至正常7V。

问:此 GVDD 5.XV 步骤是否是预期中的正常行为? 如果不是、您能否提供一些建议来确定根本原因?

谢谢。

Johnny