尊敬的 E2E 支持:

折叠数据表详细信息、无需微调 PVDD 折返功能。 通过寄存器 DSP_CTRL2 (地址= 0x3A)、一切都是自动的。

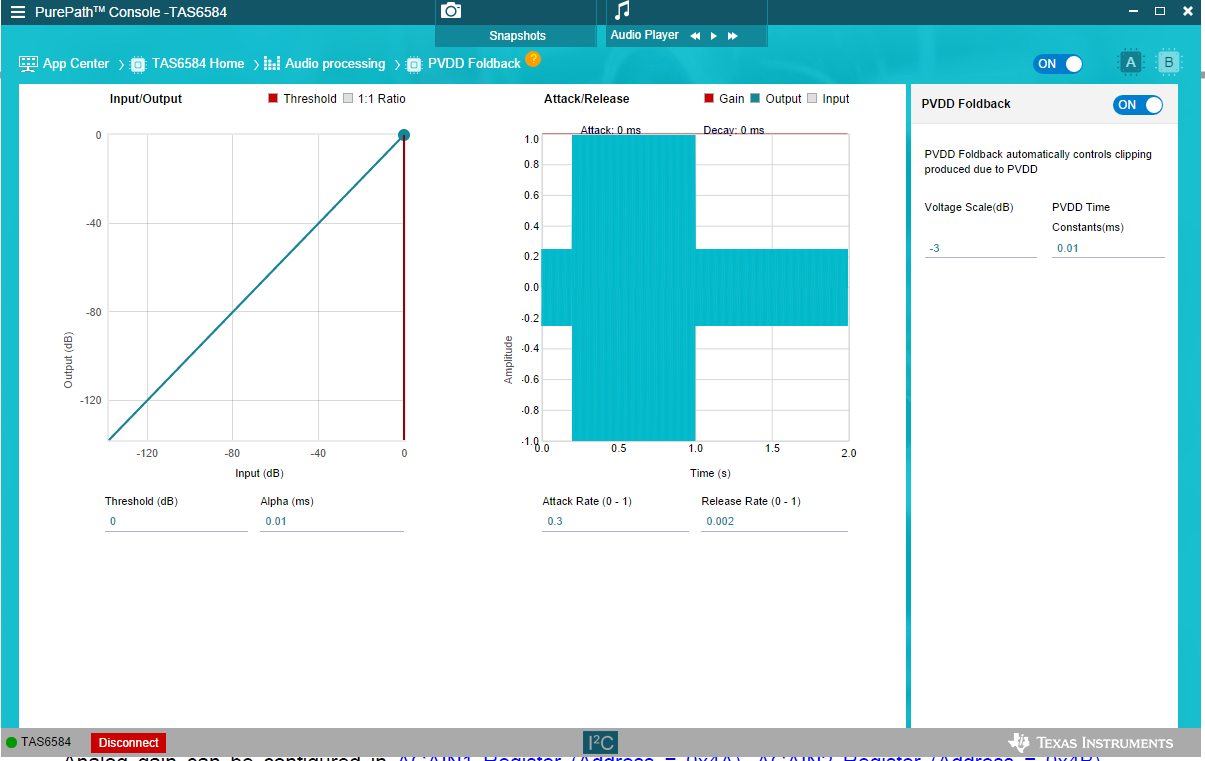

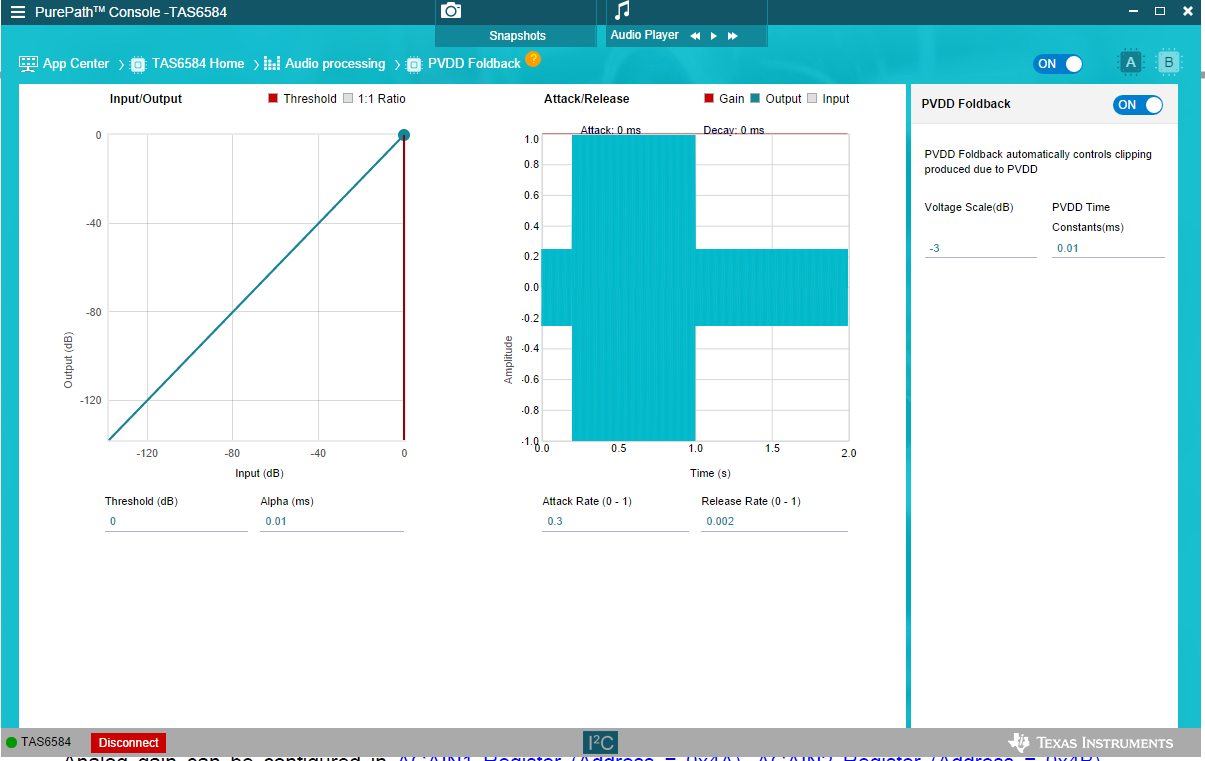

在 PCC3中、我们有一个 PVDD 折返专用部分、其中有多个参数可设置。

您能解释一下所有这些选项吗?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 E2E 支持:

折叠数据表详细信息、无需微调 PVDD 折返功能。 通过寄存器 DSP_CTRL2 (地址= 0x3A)、一切都是自动的。

在 PCC3中、我们有一个 PVDD 折返专用部分、其中有多个参数可设置。

您能解释一下所有这些选项吗?

此致、

你(们)好

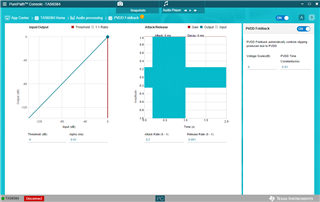

以下部分将作为正常 AGL 功能工作。 如果输出超过阈值时间超过 Alpha 时间、AGL 将生效以限制不大于阈值的最终输出。 攻击和释放意味着该功能将缓慢生效、而不是过于突然、可能会导致爆音。

以下器件与 PVDD 电压相关。 器件将检测 PVDD 电压、并使用电压标度值进行校准。 如果音频输出大于校准值的时间长于 PVDD 时间常数时间、此函数将生效以减少不大于校准值的输出。 此函数将与 AGL 共享相同的攻击和释放值。

尊敬的支持人员:

如果我 理解得好、这两个部分会实现相同的功能。 我在两个单独的窗口中看不到显著的差异。 它们中的每一个都以操作员选择的数字阈值为基准限制输出。

我认为、当启用 PVDD 折返功能时、自动将功能中的输出降低到 PVDD 电平、以限制或避免信号削波。

在产品数据表 中、SLOSE31A PVDD 折返 用以下术语表示:"如果 PVDD 电压低于 MPOV、PVDD 感应电路将降低增益、以确保信号 能够适应可用的 PVDD 电压、从而避免削波"

该函数是否如数据表中所述出现在芯片中、或者我们错误地确定了某项内容? 可以 在 PCC3软件中设置该函数吗?

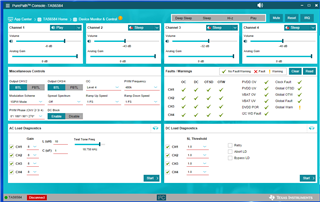

TISL 和我还询问 PVDD 折返阈值、延迟、attak 和 release 设置是否可在寄存器级别设置。 在寄存器级别、似乎只有"DSP_CTRL2寄存器(地址= 0x3A)"中的启用/禁用功能。

此致

Giacomo

你好,Giacomo

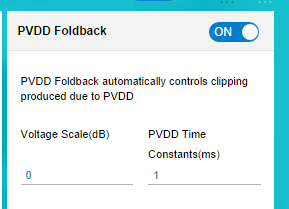

是的、这两个函数都尝试 限制最终输出。 如果我们仅对 PVDD 折返感兴趣、则可以将 阈值设置为0dB、通常将 电压标度值设置为-0.5dB、以弥补电感器和 Rdson 上的电压损耗。

[引用 userid="540206" URL"~/support/audio-group/audio/f/audio-forum/1167362/tas6584q1evm-pvdd-foldback-settings-under-ppc3/4394392 #4394394392]\n 该函数是否如数据表中所述出现在芯片中、或者我们错误地确定某项内容? 可以 在 PCC3软件中设置该函数?[/QUERP]

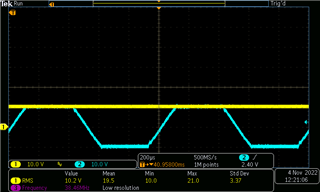

第二幅图中的 PVDD 折返正以这种方式工作。 如果器件发现输出高于 PVDD 电压、这意味着将发生削波、PVDD 折返功能将限制数字数据、从而使最终输出不削波。

[引用 userid="540206" URL"~/support/audio-group/audio/f/audio-forum/1167362/tas6584q1evm-pvdd-foldback-settings-under-ppc3/4394392 #43943943992"]TISL,我还询问 PVDD 折返阈值、延迟、attak 和释放的设置是否可在寄存器级别设置。 在寄存器级别、似乎只有"DSP_CTRL2寄存器(地址= 0x3A)"中的启用/禁用功能存在。[/引用]

抱歉、6584的流程文档尚未完成、该文档应包含详细的寄存器设置。 目前、请使用 I2C 日志函数获取寄存器设置。

嗨、 Shadow He、

感谢您的重播。

好的、澄清了 PVDD 折返是以这种方式实现的、我们必须了解我们的设置错误在哪里。

我们进行了非常简单的设置来验证 PVDD 折返功能(因为在某些不同的测试期间、我们注意到电源折返期间会发生一些削波事件)。

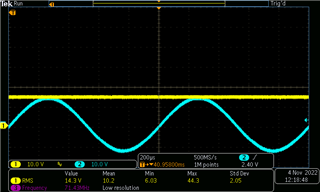

1) 1)我们将1kHz 的正弦波输入到 TAS6485EVAL 中。 PVDD 电源电压起始值为 20V。

2) 2)我们增大了输出电压、 使正弦峰值为15V。

3) 3)此时、我们开始将输出电压降低到15V 甚至更高。

为了避免削波、当 pvdd 低于15V 时、我们预计会在输出上看到 attuenation。 这种情况没有发生。 我在这里附加了设置窗口捕获以及削波的示波器捕获。

您对 我们无法看到 PVDD 折返的原因有什么看法吗?

此致

Giacomo

嗨、Shadow He、

很抱歉耽误你的回答。

好的、现在我可以成功激活 PVDD 折返功能。

我重复了预览帖子中显示的相同测试。 我们看到、在削波期间激活 PVDD 折返、OUT 信号经过缩放以消除失真。 通过改变 PVDD 电源、输出信号按比例跟随、衰减系数相同、电源轨会发生变化。

无论如何、如果音量增加、我们可以使输出再次削波到轨电压。

我没想到这一点。 我希望 PVDD 折返功能能够动态调节输出信号以及音量、以避免在增益和音量的每种情况下出现 PVDD 削波。

根据初始音量设置、PVDD 折返会使相对于电压轨电平的预设数量的输出信号衰减。

该行为是否正确? 正确的做法是,如果用户将音量更改到超过某个阈值,输出中的信号会被削波到电源轨上?

此外、衰减似乎未连接到 OUT 信号产生的有效 THD。 实际上、在菜单中应用不同的 THD 百分比量、所有级别的衰减系数都是相同的。