Other Parts Discussed in Thread: PCM1864

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1166933/pcm1864-noisy-output

器件型号:PCM1864您好!

我们正在尝试在放大器中使用 PCM1864、但是、当我们提供音频信号或不提供任何信号时、扬声器上会产生大量的白噪声和失真、我们已将其缩小为 ADC 的问题。

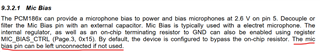

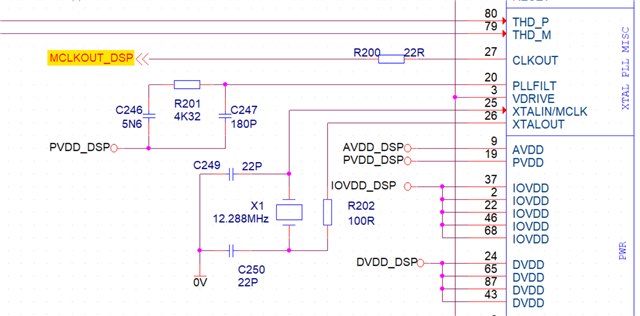

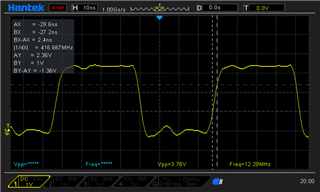

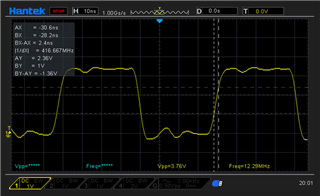

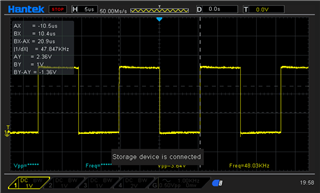

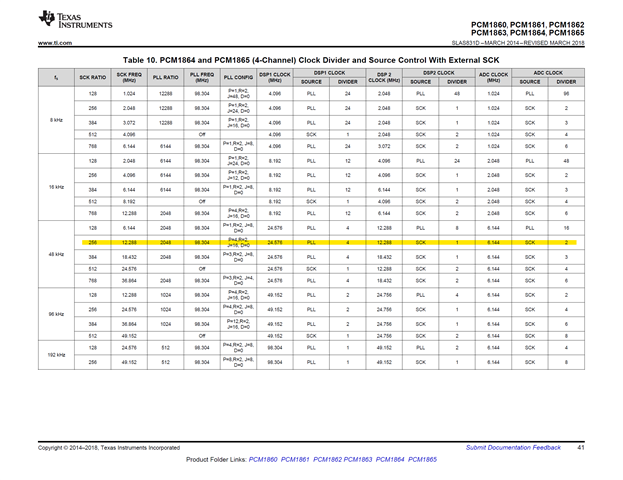

有4个 PCM1864、每个处理2对立体声输入、它们都处于从模式、由 DSP 提供时钟(SCK、BCK 和 LRCK)、由模拟器件提供 ADA1467、并且 DSP 连接到12.288MHz 晶体。 我们通过 I2C 与 ADC 进行通信、并使用它来配置 ADC 的设置。 至于 ADC 的配置、如前所述、ADC 处于从模式、我们将时钟配置为遵循数据表第41页表10的第12行、请参阅下面突出显示的内容:

我们还配置输入映射以匹配我们的硬件设置、串行音频接口格式为 TDM、4通道 TDM 传输数据和 TDM 偏移至1 bck (与 I2S 相同)、所有其他寄存器配置保留为默认值。

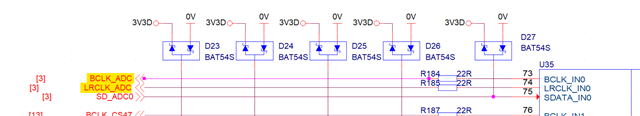

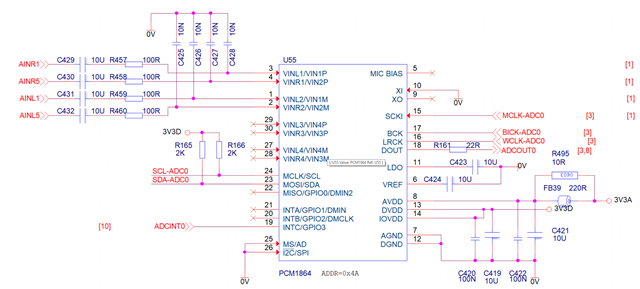

我们已经通过让 DSP 生成测试提示音来测试 ADC 以外的系统、并且提示音上没有噪声或失真、因此我们知道问题与 ADC 有关、无论是如何配置寄存器还是硬件设计。 我们的 ADC 输入设计与您的数据表中所示类似、电阻器和电容器值略有差异、但我们尝试更改这些值以匹配数据表、 但这对音频质量没有任何影响、因此我们认为问题不在于 ADC 的输入。 下面是其中一个 ADC 的原理图图片:

我们希望得到任何帮助或指示,以帮助我们解决这一问题。

谢谢你