主题中讨论的其他器件: TAS5634

您好!

我正在研发一个通过 I2S 进行数字源的放大器。 作为 PWM 接口、我使用 TAS5558。 这些放大器是采用 PBTL 封装的 TAS5634的4个部件。 我对这两种器件都有一些问题。

TAS5634:调制限制是多少? 测试条件中提到97.64%。

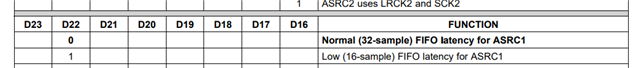

TAS5558: 我们的输入采样率为48kHz。 我们只需要从 I2S 转换为 PWM。 可通过哪些选项来最大程度地降低 TAS5558的延迟? 可以绕过 ASRC 和 DSP 吗?

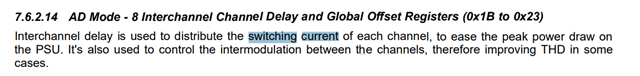

TAS5558:是否有任何选项可为通道设置不同的相位以改善 EMI 行为? 是否有任何其他选项可降低 EMI?

此致、

Markus