https://e2e.ti.com/support/audio-group/audio/f/audio-forum/736324/tlv320aic3254-tlv320aic3254

器件型号:TLV320AIC3254主题中讨论的其他器件:CC1350、

这主要是 Diego Melndez López 的问题。

他在配置 AIC 3254芯片之前帮助过我。 但是、如果其他人能帮助我解决这个问题、那将会非常有帮助。

我正在将 sinus 1000Hz 从 cc1350发送到 AIC3254。

1个案例。

当 cc1350生成 BCLK、WCLK 和数据时、AIC3254的 BCLK WCLK 和 DIN 输入上会有这样的图表。 第一行是 BCLK、第二行是 WCLK、第三行是数据。位序列有点错误、因为 BCLK 和 WCLK 正处于相反的阶段-第一个负 WCLK 前同侧是正 BCLK 前、 如果 没有位时钟反相、则不应出现这种情况。

在这种情况下、我在 AIV3254耳机输出上获得的频谱或多或少都很好

2个案例。

当 WCLK 和 BCLK 由 AIC 3254生成时、AIC3254的输入引脚上有这样的协议图片:您可以看到第一个值在 两个通道上流经数据线路、即0x00、第二个值为0001100001111110b=6270d、第三个值为0010110101000001b=11585d。

位序列正常、完全符合 图2-44。 《 TLV320AIC3254应用参考指南》第71页的 I 2S 模式时序图。

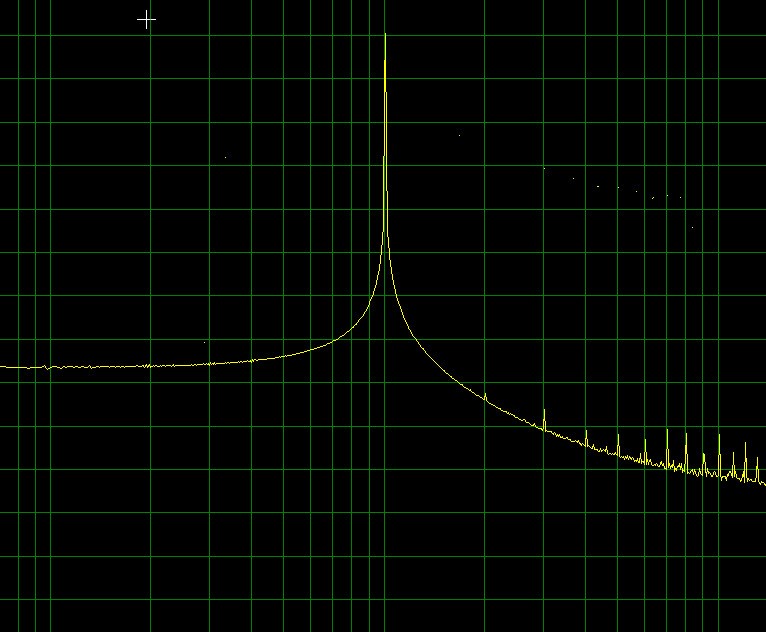

但输出频谱错误!

请告知 AIC3254参数可能有什么问题? 为什么第二种情况下的输入安全是正确的、但输出错误?

最诚挚的问候 Boris Shkarban