您好!

我们已选择您的 TLV320AIC3204编解码器与 Sierra Wireless 的调制解调器配合使用、配置它以正确与调制解调器通信时遇到一些问题。

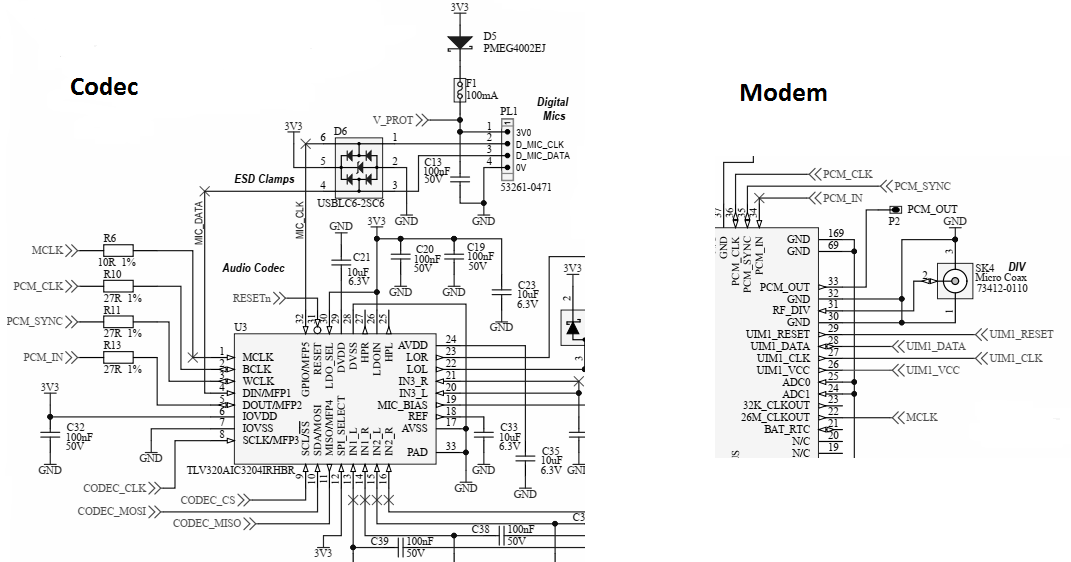

我们的系统如下:

主机微控制器要通过 SPI 设置3.3V 的编解码器、MCLK 由具有26MHz CLKOUT 引脚的调制解调器提供。 BCLK 连接到调制解调器上的调制解调器 PCM_CLK、WCLK 连接到 PCM_SYNC、DOUT 连接到 PCM_IN。

我们认为我们在设计中犯了一个错误、因为调制解调器的通用 GPIO 工作电压为1.8V、但没有提到 PCM 的电压电平、编解码器上的 IOVDD 被上拉至3.3V 以与微控制器连接。 如果您能在我们进行任何更改或调整之前确认 PCM 级别应处于 IOVDD 级别、我们将不胜感激

其次、我对编解码器进行了混合结果配置、在某些情况下、我能够振铃调制解调器、只能听到沉默、但在其他情况下、我能够听到很多白噪声。

下面是我们的启动配置、它会在调用调制解调器时产生白噪声。 如果您有任何非常感谢的建议、

PROCESSOR_Codec_WriteRegister (0x00、0x00);// Page0 Processor_Codec_WriteRegister (0x01、0x01); Processor_Codec_WriteRegister (0x12、 0x81);//将 NADC 设置为1 Processor_Codec_WriteRegister (0x13、0x82);//将 mAdc 设置为2 Processor_Codec_WriteRegister (0x14、0x80);//将 AOSR 设置为128 Processor_Codec_WriteRegister (0x3D、0x01);//选择 ADC_R1 Processor_WriteRegister (0x01、 0x01、0x0001_Codec); //将 ADC编 解码器编解码器编解码器编解码器_WriteRegister (0x01、0x01、0x01);//打开0x0001_eRegister (0x01、0x01、0x0001_eRegister (0x01);/ ELDC 编解码器 eRegister (0x01);/ E08_LDO (0x01) //将 VCM 设置为0.75V Processor_Codec_WriteRegister (0x3D、0x00);//选择 ADC PTM_R4 Processor_Codec_WriteRegister (0x47、0x32);//将 Mic PGA 设置为3.1ms Processor_Codec_WriteRegister (0x7B、0x01);//将 ref 充电时间设置为40ms Processor_Codec WriteRegister (0x02 );0x02 / UneCodec (0x20);0x02编 解码器编解码器编解码器(0x20);0xLE (0x02) // IN1_L 至 PGA_L Processor_Codec_WriteRegister (0x36、0x02);// CM_至 M_L Processor_Codec_WriteRegister (0x37、0x20);// IN1_R 至 PGA_R Processor_Codec_WriteRegister (0x39、0x02);// CM 至 M_L Processor_Codec (0x00、0x3c );0x3c 至0x3c 编解码器编解码器(0x00、0x3c) ;0x3c 至0x3c 至0x3c 编解码器 eRegister (0x00);/ Unmic Processor_eset (0x3c) //为 ADC L&R 加电 Processor_Codec_WriteRegister (0x1D、0x10);//取消 L&R Processor_Codec_WriteRegister (0x52、0x00)的静音;

参考:调制解调器设置为 PCM 主机、采样时钟边沿控制在上升沿、PCM 位时钟为512 KHz。

我的同事通过绕过 ADC/DAC 模块来配置调制解调器以将音频从 IN1_R 和 IN1_L 传递到 LOR 和 LOL、因此我们认为编解码器工作正常、只是不确定编解码器配置。

感谢你能抽出时间。