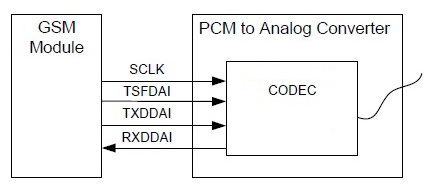

我的客户希望使用外部 I2S 总线为音频编解码器计时。 只有256kHz BLCK 存在。

它们将外部 BCLK 信号连接到 BCLK 引脚、并根据48kHz 音频的需要对其进行配置。 但该配置不起作用。

数据表中未提供 BLCK 频率限制。 同时、MCLK 限制在最低512kHz。

此器 件可接受一个介于512kHz 至50MHz 之间的 MCLK 输入、此输入随后可通过一个可编程分频器或一个 PLL 来获得器件所需的适当内部音频主时钟。 BCLK 输入也可被用于生成内部音频主时钟。

您能否澄清 BCLK 的限制?

编解码器可以从256kHz 计时?