主题中讨论的其他器件:TLV320AIC3254

工具/软件:Linux

大家好、

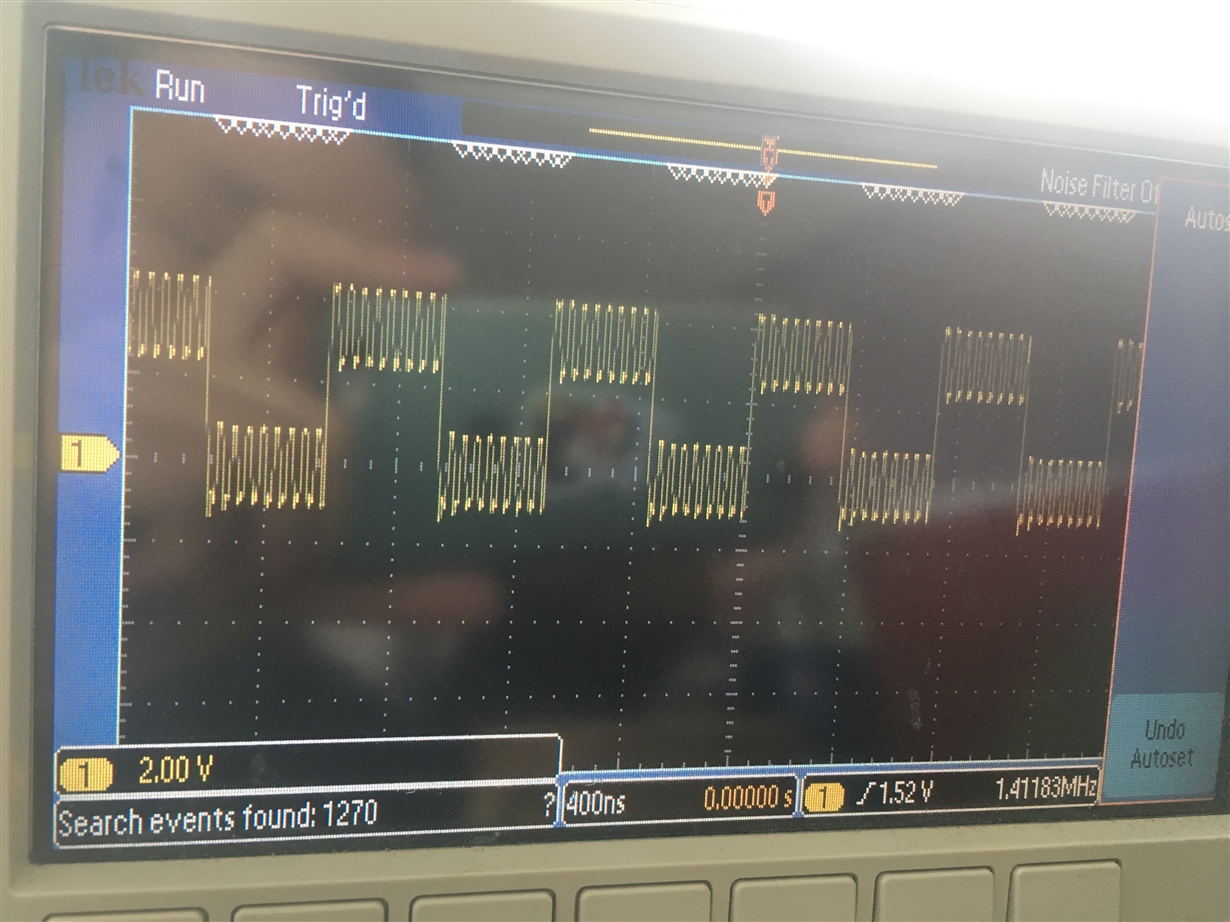

我尝试在 I2S 模式下使用具有 BeagleBone Black 的 TLV320AIC3254 E.B。 我的设置是 WCLK=44、1KHz、BCLK=1、112MHz、MCLK=24MHz、从 BBB 直接输出到这个模块上的 I2S 引脚。 下面是我通过 I2C 总线进行的配置:

e2e.ti.com/.../5722.24HMz_5F00_PLL.txt

(确保外部时钟的 sw2、4和 sw2.5关闭)。

我可以播放音乐、但听到噪音。 大家能帮我解决这个问题吗?

谢谢

Hiep Nguyen