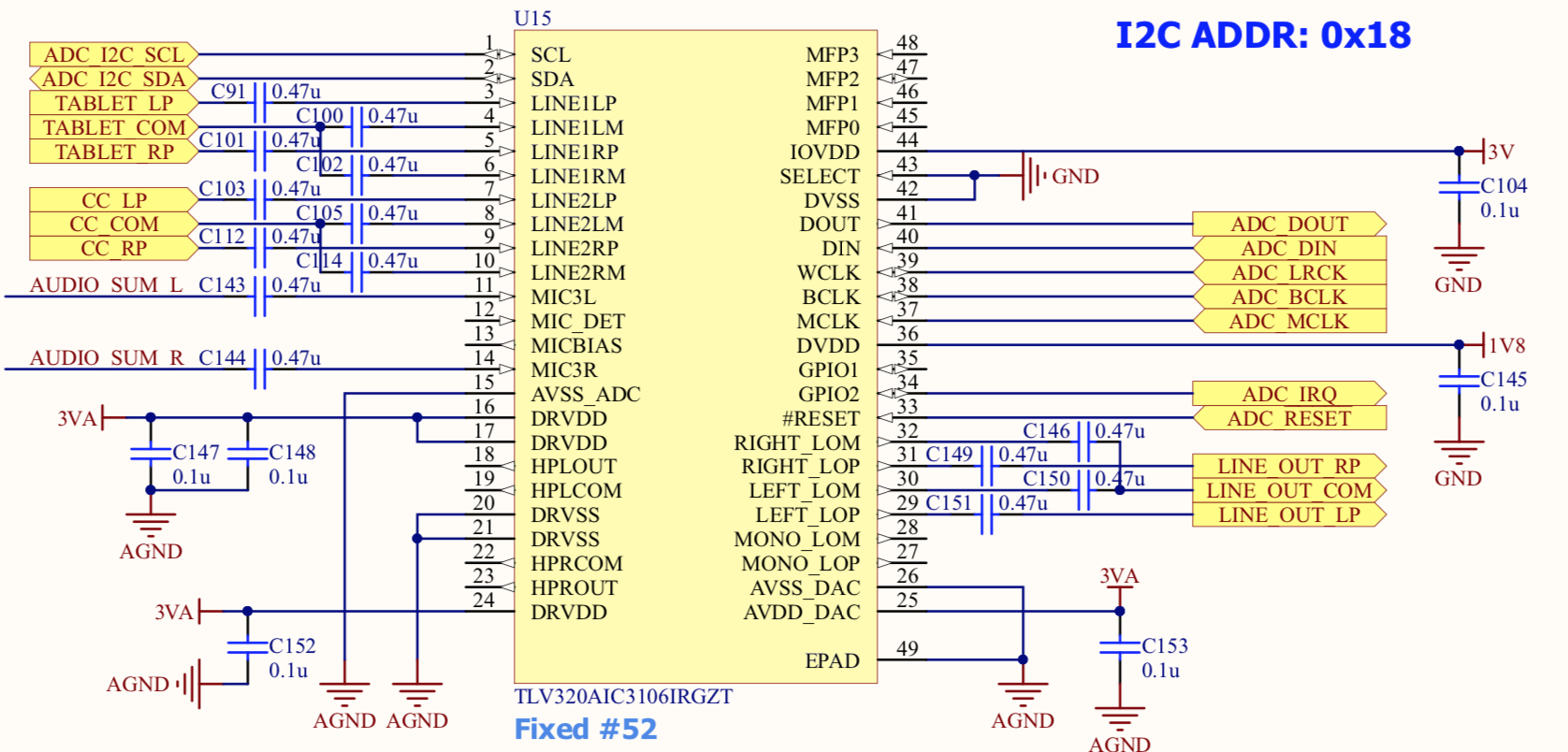

我通过 I2S 将 TLV320AIC3106从 ADC 运行到 MCU。 然后、MCU 将 I2S 上的数据镜像回 TLV320AIC3106's DAC。 我对这种行为感到困惑、因为有时当我启动它时、它确实运行良好、但大多数时候、我启动芯片时、输出中存在明显失真。

我已将其缩小到 ADC 的配置方式。 DAC 似乎正常工作、我已使用单独的 I2S 放大器验证失真是 ADC 输出 I2S 流的一部分。

下面的代码是我用于配置器件的代码。 I2S 以32位48kHz 频率运行、部件中采用48kHz*256 MCLK。 无论我使用具有 CLKDIV 的 MCLK 还是使用 PLL、我都会得到类似的结果。 一个区别是、当我运行 PLL 时、我必须清除寄存器9的低3位、否则我根本听不到任何内容。 如果我只清除寄存器9的位0、我将获得静态值。 这就是 PLL 打开时的情况。 在 PLL 关闭的情况下、寄存器9的底部3位似乎没有太大的影响。

现在、我已经对我能想到的一切进行了调整。 这个问题似乎与时钟有关、所以我在主时钟和位时钟进入编解码器时、在它们下面包括了一些示波器截图。 我无法确定我的配置是否有问题或信号完整性有问题(或者可能是电源启动?)。

谢谢!

const tlv320ae_reg_t register_values[]={

0、0x00}、//选择第0页(只有两页)

#if use_pll

{102、0x00}、//时钟控制-使用 BCLK

{3、(1<<7)|(2<<3|1)、//pll

= 1、编程1、/pll = 1、1、2、2、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1 J = 32

{5、0x00}、//PLL 编程寄存器 C - D = 0

{6、0x00}、//PLL 编程寄存器 D - D = 0

#else

{3、(2<<3)}、//Q = 2

{101、0x01}、//时钟控制-使用 MCLK -使用 CLKDIV/ CLKIN_OUT、

0x102/ CLKIN_CLK/编解码器

1<<6}、

{7、(0<5)|(1<3)|(0<1)}、//编解码器数据路径设置-双速率?、左侧 DAC ->左侧输出、右侧 DAC ->右侧输出(这可用于将输出设置为单声道)

{9、(3<<4)|(7<0

)、音频同步/音频接口(0x17)、启用音频同步/音频同步(32位)/串行接口 //MIC3L/R 输入混合左侧--来自连接至左 PGA 混合的加法放大器的左输出-单端

//{18、0xF0},//MIC3L/R 输入混合右侧--来自连接至右 PGA 混合的加法放大器的右侧输出-单端

//{20、0x80},//LINE2L 至左侧输入混合-- LINe2是 CC 输入差分-0dB 增益

//{23, 0x80},//LINE2R 到右输入混合-- LINe2是 CC 输入差分-0dB 增益

{19, 0x84},//LINE1L 到左输入混合-- Line1是平板电脑输入差分--- 0dB 增益

{22、0x84}、//LINE1R 至右侧输入混合-第1行是平板电脑输入差动- 0dB 增益

//线路输出

{37、0xC0}、//左侧 DAC 加电、右侧 DAC 加电

{41、0x00}、// DAC 输出控制-路径 L1和 R1 -独立音量控制?

{43、0x00}、//左侧 DAC 音量-未静音

{44、0x00}、//右侧 DAC 音量-未静音

{82、0x80}、//DAC_L1至 LEFT_LOP/M

{92、0x80}、//DAC_R1至 RIGHT _LOP/M

//输出

上的电源{15、0x00}、//未静音-左侧 PGA -未静音 0dB 增益(可设置为59.5dB 增益)

{16、0x00}、//右侧 PGA 未静音--- 0dB 增益(可设置为59.5dB 增益)

{86、0x09}、//LEFT_LOP/M 未静音且完全上电

{93、0x09}、//Rright_LOP/M 未静音且完全上电

{98、(2<<4)|(1<<3)}、//GPIO1具有时钟输出

、//、0x09? MONO_LOP/M 未静音且完全加电

//{94、0xD8}、//只读

//{99、(2<<4)}、// GPIO2控件-插孔/耳机检测中断-我们希望进行线性输出检测,但不确定

这是否适用于//Page 1是所有滤波器系数

};

下面是进入编解码器的位和主时钟的快照。