主题中讨论的其他器件:TLV320AIC3104

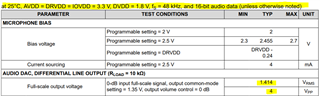

我已按照"TLV320AIC3104 Programming Made Easy (轻松编程)"中所述设置音频编解码器、并且当 LOP/M 输出控制设置>= 6dB 时差分输出会发生削波。 对于电源、 AVDD、DRVDD 和 IOVDD 采用3.3V 电源、 而 DVDD 采用1.8V 电源。 我们使用以下寄存器设置 、主要遵循"TLV320AIC3104编程速成"。

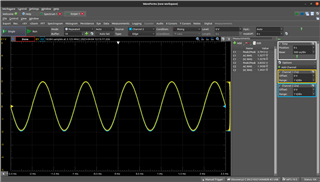

为什么在采用标准设置时、放大器设置为>= 6dB 时输出会被削波?

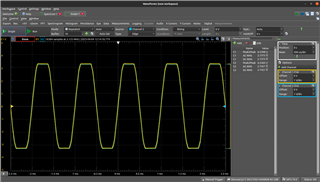

此外、当设置为0dB 时、我只能得到3.7V 峰峰值、我认为根据数据表、这应该更接近4.0V。 为什么会这样?

我附上了0dB 和9dB 的屏幕截图。