您好!

1) 1)我们的 TLV320AIC3100连接到 STM32F4 MCU、且 SAI 配置为 I2S。 DIN => DAC =>扬声器是产生适当的声音、没有任何明显的伪影。 但是、MIC => ADC => DOUT 会产生垃圾、我几乎无法理解采样的内容。 为了调试这个问题、我启用了 DIN 连接 DOUT 回送并禁用了 MIC 和扬声器。 反相 BCLK (页0、寄存器29、位3)后、DOUT 数据开始看起来与馈送到 DIN 的数据有些相似。

这是一个寄存器转储。 其余寄存器未修改。

Page..ADDR..VALUE..|7|6|5|4|3|2|1|0|

0 011...129...|1|0|0|0|0|0|0|1|

0 012...130...|1|0|0|0|0|0|0|1|0|

0 013...000...|0|0|0|0|0|0|0|0|0|0|0|

0 014...128...|1|0|0|0|0|0|0|0|0|

0 018...129...|1|0|0|0|0|0|0|1|

0 019...130...|1|0|0|0|0|0|0|1|0|

0 020...128...|1|0|0|0|0|0|0|0|0|

0 027...000...|0|0|0|0|0|0|0|0|0|0|0|

0 028...000...|0|0|0|0|0|0|0|0|0|0|0|

0 029...040...|0|0|1|0|1|0|0|0|

0 037...000...|0|0|0|0|0|0|0|0|0|0|

0 063...020.|0|0|0|0|1|1|0|0|

0 064...012.|0|0|0|0|1|0|0|

0 065...000...|0|0|0|0|0|0|0|0|0|0|0|

0 081...128...|1|0|0|0|0|0|0|0|0|

0 082...000...|0|0|0|0|0|0|0|0|0|0|

1… 032...006...|0|0|0|0|0|1|0|

1… 035...000...|0|0|0|0|0|0|0|0|0|0|0|

1… 038...127....|0|1|1|1|1|1|1|1|

1… 042...000...|0|0|0|0|0|0|0|0|0|0|0|

1… 047...000...|0|0|0|0|0|0|0|0|0|0|

1… 048...000...|0|0|0|0|0|0|0|0|0|0|

3 016...130...|1|0|0|0|0|0|1|0|

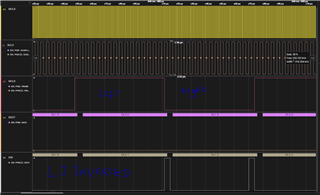

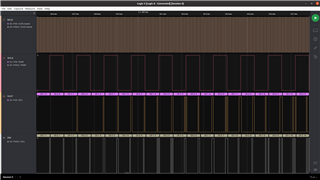

BCLK 和 WCLK 频率。

逻辑分析仪设置。

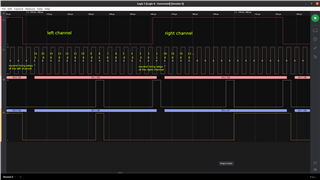

喂料1、2、3、4、5…… 并从 DOUT 读回。 BCLK 在这里反相。 您可以看到 CH2为(CH1 - 1)"Behind (后面)"。 在我看来、这似乎是一个对齐问题、因为在 TLV320AIC3100 CH2上应该等于 CH1 (单声道音频)。 您能找出问题吗?

2) 2) TLV320AIC3100能否生成主时钟? 例如、如果我启用 PLL 并将 BCLK 设置为 PLL_CLKIN、是否还需要将 MCLK 从 MCU 馈送到 TLV320AIC3100? 我主要是问的是、PLL 是否可以替代 MCLK?