请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TLV320DAC3100-Q1 主题中讨论的其他器件:TLV320DAC3100

大家好、

我们有关于 TLV320DAC3100的一些问题、我们在规格表中未找到准确的说明。

1. 引脚5、13和14是否只需要连接到相应的 SOC 引脚?

如果未使用、您需要执行上行和下行处理、还是将其保留或悬空?

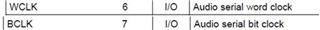

2. 当 PIN6和 PIN7连接到 SOC 时应该注意什么?

3. 如果不使用 PIN27和 PIN30、它们是需要上拉和下拉、还是可以保持悬空?

谢谢

萧祥