Other Parts Discussed in Thread: SRC4392, ADS127L01

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1234515/src4392-dir-pll1-98-304mhz

器件型号:SRC4392主题中讨论的其他器件: ADS127L01

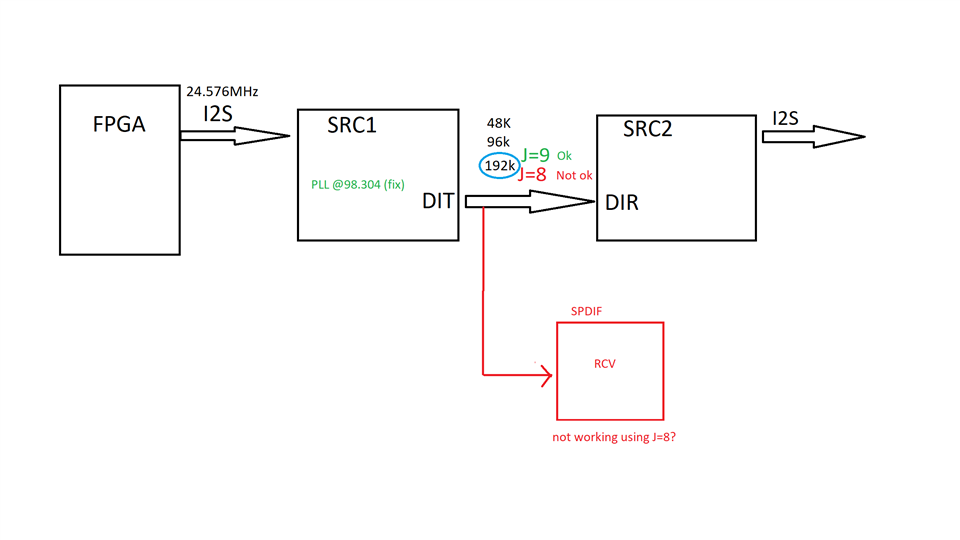

我有2个 SRC4392在相同的24.576MHz MCLK 下运行。

- 端口 A (192kHz I2S 从器件)=> SRC => DIT (48kHz、96kHz 或192kHz)

- Dir => SRC =>端口 A (192kHz I2S 从器件)

我按照 DS (P=2、J=8、D=0)中的建议配置 PLL1、以获得98.304MHz。 一切都在48kHz 和96kHz 下运行良好、但在192kHz 下、锁定是零星的、接收通道状态完全跳过;有时是正确的、有时是随机的。

如果我将 PLL1更改为110.592MHz (P=2、J=9、D=0)、192kHz 音频看起来可以正常工作。

DS 状态

寄存器0x0F 至0x11用于对 DIR 内核中的 PLL1进行编程。 PLL1将 DIR 基准时钟源乘以一个过采样率、这个速率足以满足 AES3解码器操作

然后提供尽可能接近98.304MHz 的计算量。

如果 PLL1被设定为另外一个频率、这是一个神奇频率并产生后果吗?

谢谢。

乔恩