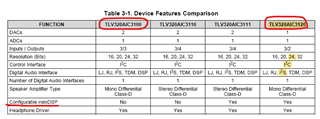

主题中讨论的其他器件: TLV320AIC3111、 TLV320AIC3100

我正在尝试像这样对它进行设置。

外部输入在 FPGA 中作为 I2S 流工作。

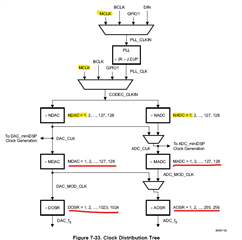

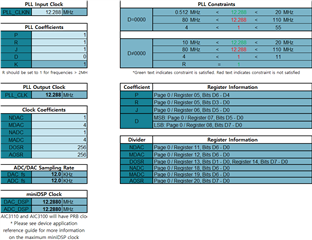

MCLK=12.288Mhz、ADC/DAC = 12kHz

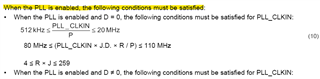

1) 1) 不使用 PLL。 那么、 我可以忽略 PLL 约束吗?

我可以使用以下设置吗?

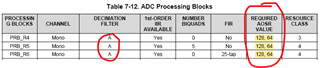

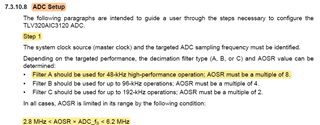

NADC:1 / mADC:4 / AOSR:256 / ADC_FS:12 kHz

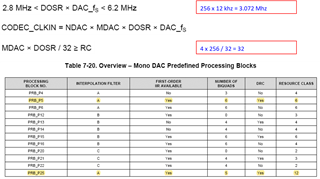

NDAC:1/MDAC :4/AOSR:256/DAC_fs:12kHz

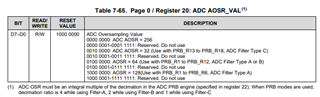

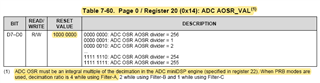

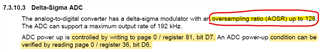

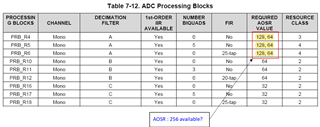

2) AOSR: 256,有可能吗?

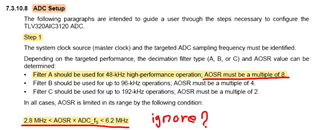

2.8Mhz <= AOSR x ADC_FS <= 6.2Mhz

因此、AOSR 应为256。

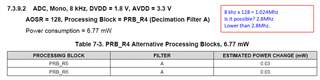

3) 3) 我想使用 PRB_R4、R5、R6。 AOSR 必须是128? 我可以使用256吗?

4) 4) 将使用具有 DRC 功能的 PRB_R25、P5。

我可以使用上面的设置吗?

FPGA 的 IP 配置为 I2S 通信、频率为256×Fs。

所以最好以设定的时钟运行。 是否可以将其与上述设置一起使用?

如果有其他更好的设置、请更正。