Other Parts Discussed in Thread: LM4550B

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1257471/lm4550b-lm4550b-codec

器件型号:LM4550B

上面是 ADSP 处理器和 LM4550B 编解码器之间的接口。

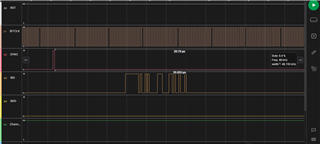

问题:当编解码器退出复位并成功接收到 SYNC 时、虽然预计会有 BITCLK 和 SYNC 频率、但它不会生成 CODEC_READY 位1 (时隙0、位15)。

下面是波形。

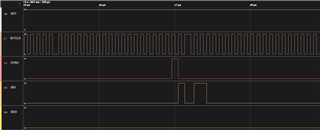

我们正在由 Tempo Semiconductors 验证我们相对于 AC97链路协议编解码器 STAC9753的代码、并且我们正在获取预期的 CODEC_READY 位1 (时隙0、位15)、下面是 STAC9753的波形。

注意:LM4550B 在寄存器和通信协议方面可直接替代 STAC9753。

谢谢!