大家好!

抱歉、我需要更多说明或帮助。

GUI 上的示例预设用于44.1kHz 的使用。

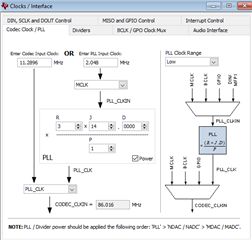

我想使用48kHz 和相当 低的2.048MHz MCLK 频率。 (这是 从 MCU 传输到 我电路板上 DAC 的 MCLK 引脚的频率)

顺便说一下、GUI 实际上不必"工作"、而只能用作某种脚本生成器。

表2-23 (SLAU434A 上的第66页)显示了 下列相关寄存器值:

// Fs = 48kHz 时的 PLL 配置

// MCLK (MHz) PLLP PLLJ PLLD 调节 NADC AOSR MDAC NDAC DOSR

// 2.048 1 3 14 0 2 7 128 7 2 128

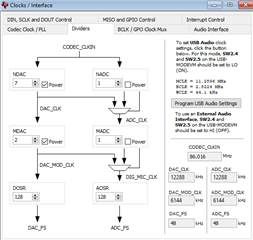

我希望使用 GUI 来安全地配置所有这些、但无法实现所需的48kHz 采样率 fs

根据表中的值、我得到 DAC_FS = 48.7619kHz、

直接写入寄存器是的、我可以尝试、但依靠 GUI 会感觉更舒适。

您能指导我完成这一过程吗?

此致、

古斯塔沃