Other Parts Discussed in Thread: PCM5121

大家好、

对于硬件主模式、BCLK 和 LRCLK 由 PCM512x 芯片组供电、

PCM512x 如何知道什么 FS 是时钟由 LRCLK ,因为有几个选择.

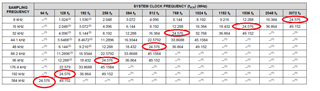

例如:当 SCK 由24.576MHz 供电时、PCM512x 如何知道 LRCLK 的频率被认为是48kHz (512fs)、96KHz (256fs)或384KHz 64fs)?

PCM512x 在硬件模式下是否仅接受32位音频深度?

谢谢。

此致、

欧内斯特