您好,

我们的客户将 TLV320ADC3101-Q1用于其应用、采样率为32Kbps、 从 BCLK 生成了主时钟、

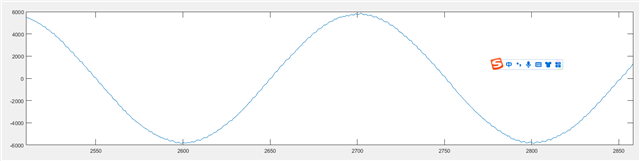

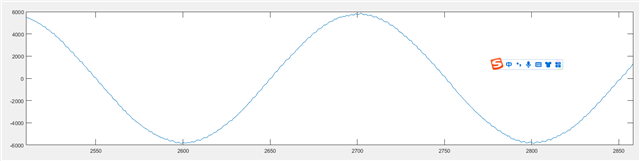

利用 MATLAB 进行绘制的 ADC 输出的捕获数据 不平滑、因为:

此致

凯林

但如果配置为16Kbps 采样率、则捕获的曲线是平滑的。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

我们的客户将 TLV320ADC3101-Q1用于其应用、采样率为32Kbps、 从 BCLK 生成了主时钟、

利用 MATLAB 进行绘制的 ADC 输出的捕获数据 不平滑、因为:

此致

凯林

但如果配置为16Kbps 采样率、则捕获的曲线是平滑的。

数字化正弦波不是一个平滑的曲线。

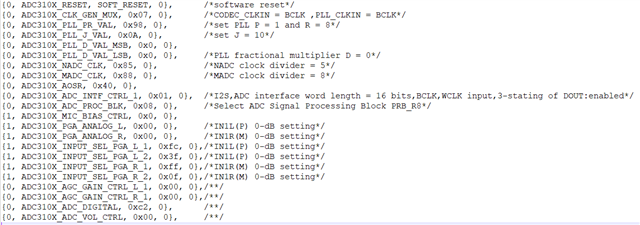

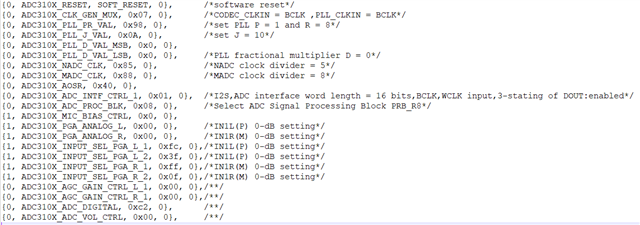

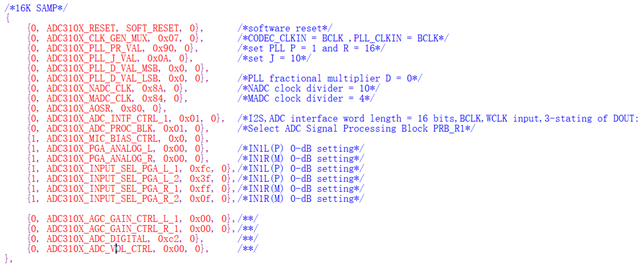

系统时钟从 BCLK 生成主时钟, 如下图所示的寄存器配置:

使用此公式计算参数:FS=(PLLCLK_IN×K×R)/(NADC×mAdc×AOSR×P)

BCLK:32000*16*2=1024kHz,

P=1,R=8,K=10.0,NADC=5,mAdc=8,AOSR=64,μ A

FS=(1024 x 10 x8)/(5 x 8 x 64 x 1)=32k

ADC 处理块为 PRB_R8。

尊敬的 Jiameng:

只是为了澄清一下、客户看到16kHz 采样时输出平滑、而 32kHz 采样时曲线失真?

备注:

此致、

只是为了澄清一下,客户看到16kHz 采样时输出平滑,而 32kHz 采样时曲线失真?--是的。

备注:

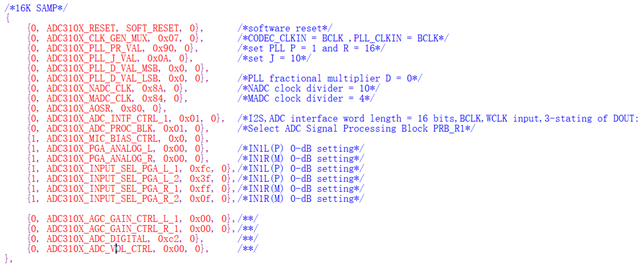

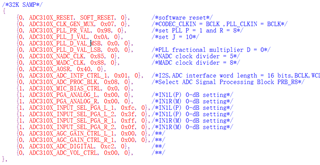

-否,差约16kHz 和32kHz, 如下:

| 16kHz | 32 kHz | |

| 采样率(Hz) | 16000 | 32000 |

| BCLK (Hz | 512000 | 1024000 |

| P | 1 | 1 |

| R | 16 | 8 |

| k | 10 | 10 |

| NADC | 10 | 5 |

| MADC | 4 | 8 |

| AOSR | 128 | 64 |

| PRB_R | PRB_R1 | PRB_R8 |

| FS | (512 x 10 x16)/(4 x 10 x 128 x 1)=16k | (1024 x 10 x8)/(5 x 8 x 64 x 1)=32k |

尊敬的 Jiameng:

您的寄存器配置和分频器看起来是正确的。 我有两个建议:

此致、