您好!

AIC3204通过以下测试条件指定输入通道间隔。

3dBFs 时1kHz 正弦波输入

单端配置

IN1_L 路由到左侧 ADC

IN1_R 路由到右侧 ADC、RIN = 20kΩ

AGC =关闭、AOSR = 128、

通道增益= 0dB、CM = 0.9V

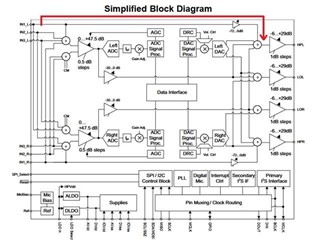

由于 AIC3204可以将模拟输入直接路由到模拟输出、因此我们对输入与输出的分离感兴趣。

数据表未提及任何有关 IN1_x 和输出之间隔离的内容。

如果 IN1_x 与输出的隔离未知、那么我们也对 IN2_L 与 IN2_R 之间的隔离与 IN1_L 和 IN1_R 的规格相同(108dB)感兴趣、因为仅为 IN1_L 和 IN1_R 指定了输入通道的隔离。